Qucs-S a maturing GPL software package for circuit simulation and compact modelling of current and emerging technology devices

> Mike Brinson <sup>1</sup>, mbrin72043@yahoo.co.uk. Vadim Kuznetsov <sup>2</sup>, ra3xdh@gmail.com

<sup>1</sup>Centre for Communications Technology, London Metropolitan University, UK <sup>2</sup>Bauman Moscow Technical University, Russia

### Qucs-S a maturing GPL software package: Introduction to presentation

- $\bullet$  Background and release dates for Qucs-S/RC7

- Qucs-S documentation and circuit simulation capabilities

- Qus-S Help documentation: User manual and reference material,

- Qucs-S SPICE style components and model libraries,

- Qucs-S extended circuit simulation features.

- Qucs-S Equation-Defined Device (EDD) and Verilog-A compact device modelling case studies

- The Efficient Power Corporation (EPC) GaN EPC2001 power transistor model,

- The MIT virtual source GaN-RF HEMT 1.0.0 model.

- Qucs-S modelling tool extensions and new features

- XSPICE "Code Model" support,

- Qucs-S model parameter extraction controlled by Qctave script files.

- Qucs-S future developments the way forward in 2016-2017

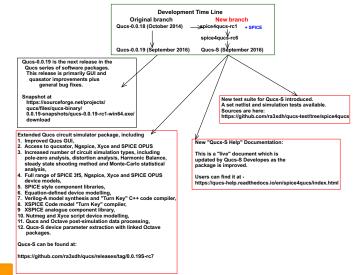

#### Qucs-S a maturing GPL software package: Background and release details

#### Qucs-S a maturing GPL software package: Latest release impact

#### Screenshots

#### Description

Ques is an integrated circuit simulator which means you are able to setup a circuit with a graphical user interface (GUI) and simulate the large-signal, small-signal and noise behaviour of the circuit. After that simulation has finished you can view the simulation results on a presentation page or window. Supports spice simulators.

#### Changelog

After install run in terminal: snap run qucs-spice.qucs

#### Permissions

- Home

- Unity7

#### Info

Support: https://github.com/eldarkg/qucs-spice-snap/issues Website: http://qucs.sourceforge.net

Version: 0.0.19S-RC7-snap2 Updated: Sep 5, 2016 Published: Sep 4, 2016 License: GNU GPL v2 File Size: 89-2 MB Architectures: 1386, amd64

#### MORE INFO

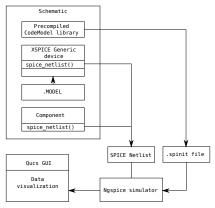

### Qucs-S a maturing GPL software package: Functional block diagram

### Qucs-S a maturing GPL software package: Qucs-S Help documentation

#### Search doc

#### Chapter 1. Introduction

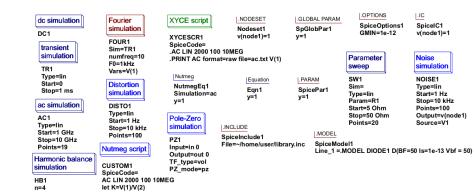

Chapter 2. Basic Ngspice, Xyce and SPICE OPUS simulation

Chapter 3. Spice4ques subcircuits, macromodels and device libraries

Chapter 4. Device and component modelling with algebraic equations

Chapter 5. More advanced circuit simulation techniques.

Chapter 6. Ngspice, Xyce and SPICE OPUS post-simulation data processing with Qucs-S and Octave

Chapter 7. Qucs and SPICE simulation models that work with ngspice, Xyce and SPICE OPUS

Chapter 8. Ngspice custom simulation technology

Chapter 9. XSPICE standard components and library

Chapter 10. XSPICE user written device models and library

Chapter 11. Introduction to mixed analogue/digital simulation

Chapter 12. Verilog-A compact semiconductor device modelling

Chapter 13. RF simulation with Ngspice, Xyce and SPICE OPUS

Chapter 14. Qucs-S/Octave circuit simulation and device parameter extraction interface

Chapter 15. References

#### **Qucs-S Help documentation**

#### **User Manual and Reference Material**

Authors Mike Brinson (mbrin72043@yahoo.co.uk) and Vadim Kusnetsov (ra3xdh@gmail.com)

Copyright 2015, 2016

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation. A copy of the license is included in the section entitled "GNU Free Documentation License."

#### Contents:

- Chapter 1. Introduction

- Chapter 2. Basic Ngspice, Xyce and SPICE OPUS simulation

- Chapter 3. Spice4ques subcircuits, macromodels and device libraries

- · Chapter 4. Device and component modelling with algebraic equations

- Chapter 5. More advanced circuit simulation techniques.

- Chapter 6. Ngspice, Xyce and SPICE OPUS post-simulation data processing with Qucs-S and Octave

- Chapter 7. Quos and SPICE simulation models that work with ngspice, Xyce and SPICE OPUS

- Chapter 8. Ngspice custom simulation technology

- Chapter 9. XSPICE standard components and library

- Chapter 10. XSPICE user written device models and library

- Chapter 11. Introduction to mixed analogue/digital simulation

- Chapter 12. Verilog-A compact semiconductor device modelling

- Chapter 13. RF simulation with Ngspice, Xyce and SPICE OPUS

- · Chapter 14. Qucs-S/Octave circuit simulation and device parameter extraction interface

- Chapter 15, References

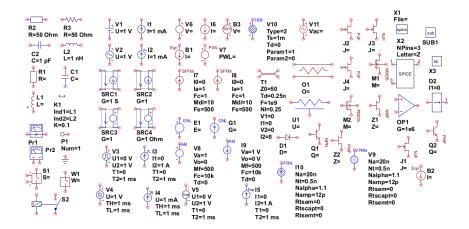

# Qucs-S a maturing GPL software package: Ngspice, Xyce and SPICEOPUS built in components

# $\mathsf{Qucs}\text{-}\mathsf{S}$ a maturing GPL software package: Available semiconductor device models

| Туре          | Description                 | Level               | Ngspice | Хусе        | SPICEOPUS |

|---------------|-----------------------------|---------------------|---------|-------------|-----------|

| D             | Legacy                      | 1<br>2              | x       | x           | x         |

|               |                             | 3                   |         |             | x         |

| BJT           | Legacy<br>VBIC<br>FBH HBI X | 1<br>10,11,12<br>23 | x       | X<br>X<br>X | x         |

|               | MEXTRAM                     | 504,505             |         | ~           | х         |

| JFET          |                             | 1                   | х       | х           | x         |

|               |                             | 2                   | x       | х           | x         |

| MESFET        |                             | 1 (Statz)           | x       | х           | x         |

|               |                             | 2 (Ytterdel)        | x       |             |           |

| MOSFET Legacy |                             | 1                   | х       | х           | х         |

|               |                             | 2                   | х       |             | x         |

|               |                             | 3                   | х       | х           | х         |

|               |                             | 4(BSIM1)            | х       |             | х         |

|               |                             | 5(BSIM2)            | х       |             | х         |

|               |                             | 6                   | x       | х           | x         |

|               | BSIM3v2                     | 47                  |         |             | x         |

|               | Bolinisva                   | 8                   | х       |             | ^         |

|               |                             | 9                   | ~       | х           |           |

|               | BSIM3v3                     | 53                  |         | ^           | x         |

|               | DOIMIDVD                    | 49                  | х       |             | ^         |

|               |                             |                     | ^       |             |           |

| BSIM4         |                             | 60                  |         |             | x         |

|               |                             | 14                  | x       | х           |           |

|               |                             | 54                  | х       |             |           |

|               | BSIM3SOIv1                  | 55                  |         |             | x         |

|               | BSIMOIv2                    | 56                  | х       |             | х         |

|               |                             | 58,55,57            | х       |             |           |

|               |                             | 10                  | х       | х           |           |

|               | STAGSO13                    | 57                  |         |             | х         |

| UFSOI         |                             | 58                  |         |             | х         |

|               | SOI3                        | 60                  | х       |             |           |

|               | UFET                        | 7                   |         |             | x         |

|               | EKVv2p6                     | 44                  | х       |             | x         |

|               | HISIM2                      | 61.68               | x       |             |           |

|               | HISIM HV                    | 62,63               | â       |             |           |

|               | VDMOS                       | 18                  | ~       | х           |           |

|               | BSIM 6p1                    | 77                  |         | â           |           |

|               | PSP 103p1                   | 103                 |         | â           |           |

|               | For Nopl                    | 105                 |         | ^           |           |

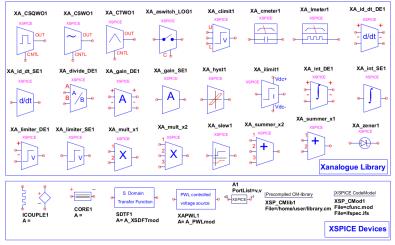

### Qucs-S a maturing GPL software package: XSPICE analogue component models

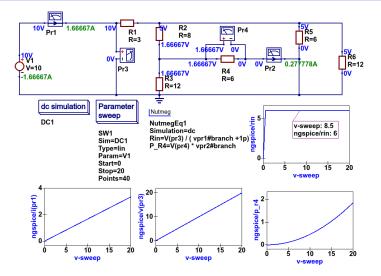

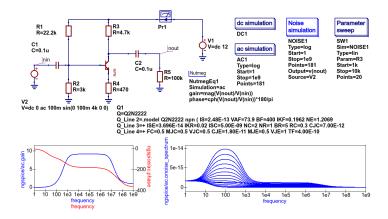

# Qucs-S a maturing GPL software package: Qucs-S extended circuit simulation Part 1. SPICE .OP to visual DC by pressing key "F8"

### Qucs-S a maturing GPL software package: Qucs-S extended circuit simulation Part 2. Noise spectral response

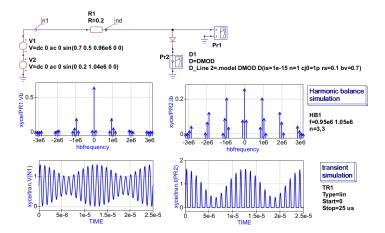

# Qucs-S a maturing GPL software package: Qucs-S extended circuit simulation Part 3. Multi-tone Harmonic balance analysis

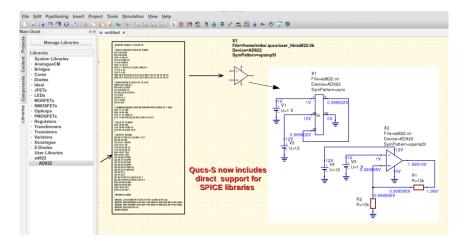

### Qucs-S a maturing GPL software package: Qucs-S extended circuit simulation Part 4. Direct support for SPICE libraries

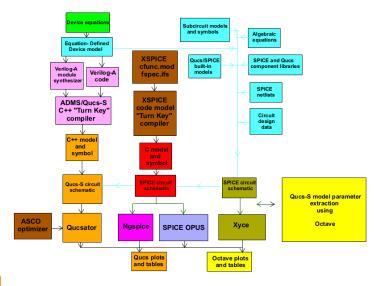

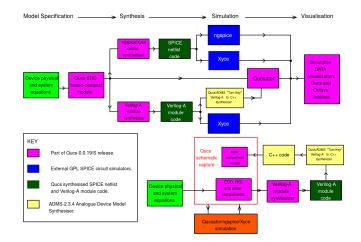

Qucs-S a maturing GPL software package: Compact device modelling tools Part 1. Equation-Defined behvioural modelling and Verilog-A model code synthesis

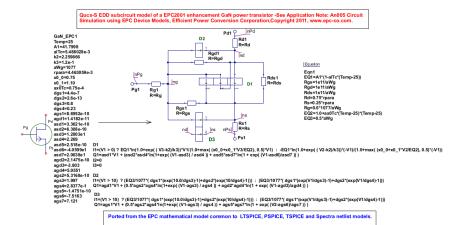

# Qucs-S a maturing GPL software package: Compact device modelling Part 2. Qucs-S EDD model of the Efficient Power Corporation (EPC) GaN EPC2001 power transistor

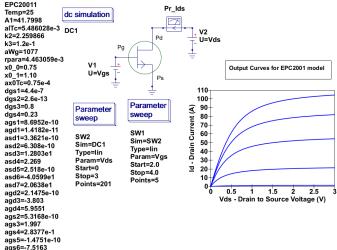

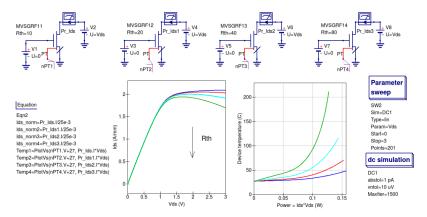

Qucs-S a maturing GPL software package: Compact device modelling Part 3. Qucs-S EDD model of the Efficient Power Corporation (EPC) GaN EPC2001 power transistor; DC test bench and typical output simulation curves

- X - O

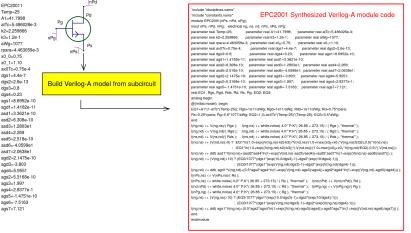

### Qucs-S a maturing GPL software package: Compact device modelling Part 4. Synthesis of Verilog-A code for the Efficient Power Corporation (EPC) GaN EPC2001 power transistor

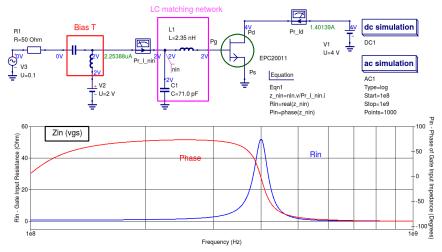

# Qucs-S a maturing GPL software package: Compact device modelling Part 5. AC gate matching network, test bench and typical simulation results

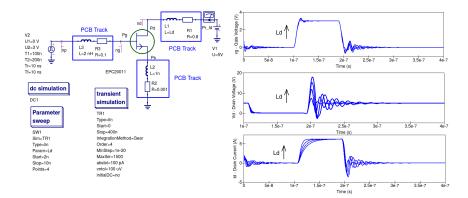

# Qucs-S a maturing GPL software package: Compact device modelling Part 6. Switching response test bench and typical simulation results

Qucs-S a maturing GPL software package: Verilog-A modeling of the MIT virtual source GaN-RF HEMT 1.0.0: Problems simulating with ADMS; workarounds and typical simulationdData - Part 1. Introduction

- The Analogue Device Model Synthesizer (ADMS) version 2.3.5 is used by Qucs/Qucs-S, Ngspice, Xyce and Gnucap GPL circuit simulators.

- ADMS is based on a subset of Verilog-A HDL selected for compact device modelling.

- Although the Verilog-A HDL is standardised there is no guarantee that individual simulator implementations allow the same dialect of Verilog-A for modelling purposes, for example Qucs/Qucs-S Verilog-A models can include component noise while Ngspice does not implement thermal, shot or flicker noise.

- Normally emerging technology Verilog-A compact models have to be modified, often by hand, to compile without error: specific areas which can cause problems are

- Internal node collapsing,

- Voltage limiting,

- Setting initial conditions,

- Model equations that include complex combinations of analogue functions,

- Thermal effects due to power dissipation.

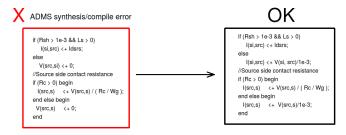

Qucs-S a maturing GPL software package: Verilog-A Modeling of the MIT Virtual Source GaN-RF HEMT 1.0.0: Problems simulating with ADMS; workarounds and typical simulation data - Part 2. Model parameter statement error workarounds

ADMS parameter statements DO NOT ALLOW reference to previously defined model parameters.

ADMS synthesis/compile error

| parameter real | word     | - 1,30e  | 7 from (0:inf); | // Source injection velocity [cm/s]                         |

|----------------|----------|----------|-----------------|-------------------------------------------------------------|

| parameter real |          | = -2.0:  |                 | id voltage of drain access transistor[V]                    |

| parameter real |          | - 5.0e-7 | from (0:inf):   | // Drain access areal capacitance [F/cm2]                   |

|                |          |          |                 |                                                             |

| parameter real |          |          | from (0:inf);   | // DIBL for drain access transitor                          |

| parameter real | delta2rd | = 0.30   | from [0:inf);   | // DIBL for drain access transitor                          |

| parameter real | Vdibsat  | = 2.0    | from (0:inf);   | // DIBL for drain access transitor                          |

| parameter real | Srd      | = 0.35   | from (0:inf);   | // Subthreshold slope for drain access transitor [V/Dec]    |

| parameter real | zeta     | - 0.0    | from (0:inf);   | // Self heating parameter (scalable)                        |

| parameter real | betard   | = 1.3    | from (0:inf);   | // Linear to saturation transition parameter                |

| parameter real | vthetard | - 0.05   | from (0:inf);   | // Scattering: velocity reduction parameter with Vg         |

| parameter real | ndrd     | = 0*0.80 | from (0:inf);   | // Punchthrough factor affects slope change in subthreshold |

| parameter real | vxors    | - vxord  | from (0:inf);   | // Source injection velocity [cm/s]                         |

| parameter real | VtOrs    | = VtOrd; | // TI           | hreshold voltage of drain access transistor[V]              |

| parameter real | Cgrs     | - Cgrd   | from (0:Inf);   | // Drain access areal capacitance [F/cm2]                   |

| parameter real | delta1rs | - delta1 | d from (0:inf); | // DIBL for drain access transitor                          |

| parameter real | delta2rs | - delta2 | d from (0:inf); | // DIBL for drain access transitor                          |

| parameter real | Srs      | = Srd    | from (0:inf);   | // Subthreshold slope for drain access transitor [V/Dec]    |

| parameter real | vthetars | = 0.05   | from (0:inf);   | // Scattering: velocity reduction parameter with Vg         |

| parameter real | ndrs     | - ndrd   | from (0:Inf);   | // Punchthrough factor affects slope change in subthreshold |

| parameter real | betars   | = betard | from (0:inf);   | // Linear to saturation transition parameter                |

#### OK

| parameter real | vxord    | = 1.30e  | 7 from [0:inf); |

|----------------|----------|----------|-----------------|

| parameter real | VtOrd    | = -2.0;  |                 |

| parameter real | Cgrd     | = 5.0e-7 | from (0:inf);   |

| parameter real | delta1rd | = 1.3    | from [0:inf);   |

| parameter real | delta2rd | = 0.30   | from [0:Inf);   |

| parameter real | Vdibsat  | = 2.0    | from [0:inf);   |

| parameter real | Srd      | = 0.35   | from [0:inf);   |

| parameter real | zeta     | = 0.0    | from (0:inf);   |

| parameter real | betard   | = 1.3    | from (0:inf);   |

| parameter real | vthetard | = 0.05   | from [0:Inf);   |

| parameter real | ndrd     | = 0.80   | from (0:inf);   |

|                |          |          |                 |

| parameter real | VtOrs    | = -2.0;  |                 |

| parameter real | Vxors    | = 1.30e7 |                 |

| parameter real | Cgrs     | = 5.0e-7 | from (0:Inf);   |

| parameter real | delta1rs | = 1.3    | from [0:inf);   |

| parameter real | delta2rs | = 0.30   | from [0:inf);   |

| parameter real | Srs      | = 0.35   | from [0:inf);   |

| parameter real | vthetars | = 0.05   | from [0:inf);   |

| parameter real | ndrs     | = 0.80   | from [0:inf);   |

| parameter real | betars   | = 1.3    | from (0:inf);   |

|                |          |          |                 |

Qucs-S a maturing GPL software package: Verilog-A Modeling of the MIT Virtual Source GaN-RF HEMT 1.0.0: Problems simulating with ADMS; workarounds and typical simulation data - Part 3. Removing V(n) < +statements

- ADMS DOES NOT ALLOW voltage contributions of the form V(n) < +I(n)R, where R is a resistance in  $\Omega$ ,

- OR statements of the form V(n) < +0.0,

- Resistors, for example 0.001, are used to short nodes (node collapsing), with I(n) < +V(N)/0.001.

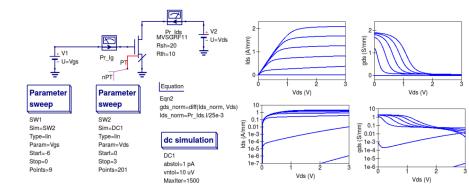

Qucs-S a maturing GPL software package: Verilog-A Modeling of the MIT Virtual Source GaN-RF HEMT 1.0.0: Problems simulating with ADMS; workarounds and typical simulation data - Part 4. DC characteristics

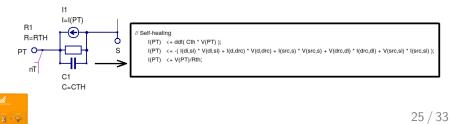

Qucs-S a maturing GPL software package: Verilog-A Modeling of the MIT Virtual Source GaN-RF HEMT 1.0.0: Problems simulating with ADMS; workarounds and typical simulation data - Part 5. Simulating thermal self-heating effects induced by internal power dissipation

- The ADMS dialect of Verilog-A does not implement the *pwr(dt)* statement,

- Device self-heating is often modelled with a parallel RC network where the volt drop across the RC combination represents the change in device temperature due to internal power dissipation,

- Tth = RthPd + Temp(Pd = 0), where Tth is the device temperature at power dissipation Pd(W).

Qucs-S a maturing GPL software package: Verilog-A Modeling of the MIT Virtual Source GaN-RF HEMT 1.0.0: Problems simulating with ADMS; workarounds and typical simulation data - Part 6. Variation of thermal resistance *Rth* and its effect on DC characteristics

- Qucs-S includes for the first time a turn-key XSPICE "code level modelling" package for use with the Ngspice and SPICE OPUS circuit simulators,

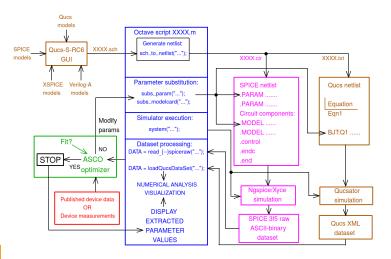

- Qucs-S has also been extended to include a new Qucs/Octave integrated tool set for compact device model and circuit macromodel parameter extraction. The technique employed is based on data fitting and optimization using measured, or manufacturers published device data, compared against simulated circuit data.

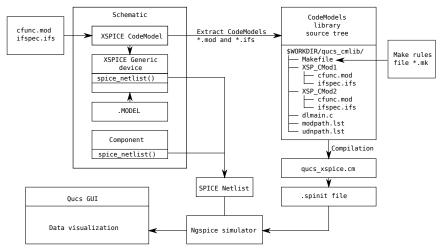

### Qucs-S a maturing GPL software package: XSPICE "Code Model" support subsystem

- The XSPICE generic device component is the foundation for

- Precompiled XSPICE device (\*.cm) library support, and

- Dynamic XSPICE "Code Model" compilation system which allows Code Model sources to be attached to a schematic and compiled automatically at simulation time.

### Qucs-S a maturing GPL software package: XSPICE Generic Device component

• The XSPICE generic device component is a building block for the construction of user-defined A-devices. It is defined by a comma separated port list, plus XSPICE port designators. These are attached to a SPICE .MODEL statement

# Qucs-S a maturing GPL software package: XSPICE Turn-Key Model Generation; compiler system dataflow diagram

Qucs-S a maturing GPL software package: Ngspice/Xyce/SPICEOPUS device parameter extraction from maufacturers data, or measurements, controlled by Octave Script Files; structure diagram

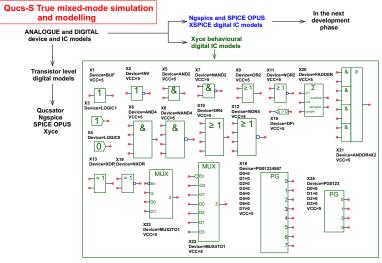

# Qucs-S a maturing GPL software package: Future developments - the way forward in 2016-2017

- Qucs-S is a relatively stable circuit simulator and compact modelling tool, incorporating the best features of Qucs, Ngspice. Xyce and SPICE OPUS. The next development phase will concentrate on the following:

- Testing the package and improving the "feature coverage" by the Qucs-S test suit,

- Adding the missing sections to the "Qucs-S Help" documentation,

- Introduction of XSPICE and Xyce digital models as the first step towards making Qucs-S a true mixed-mode electronic system and circuit simulation and modelling package,

- Improvements to XSPICE CodeModel development system, including new XXX.mod and XXX.ifs templates generated from model schematics,

- Continue development of the Qucs-S built-in libraries.

- It is expected that the next development phase will last around one year with a series of release candidates published at regular intervals.

### Qucs-S a maturing GPL software package: Endnote - A brief look into the future