## Ques Roadmap: background to the new features in release 0.0.18 and an outline of future software development directions

**Mike Brinson**, Centre for Communications Technology, London Metropolitan University, UK, mbrin72043@yahoo.co.uk.

Richard Crozier, The University of Edinburgh, UK, richard.crozier@yahoo.co.uk.

Clemens Novak, Qucs Developer, clemens@familie-novak.net.

Bastien Roucaries, Laboratoire SATIE – CNRS UMR 8929, Université de Cergy-Pontoise, ENS Cachan, FR, bastien.roucaries@satie.ens-cauchan.fr.

Frans Schreuder, Nikhef, Amsterdam, NL, fransschreuder@gmail.com.

Guilherme Brondani Torri, Qucs Developer, guitorri@gmail.com.

Plus contributions from Developers in the Qucs user community.

Listed in "Projects of the week", September 8, 2014, by Sourceforge.

- Qucs release 0.0.18: an overview of new simulation and compact device modelling features

- Compact model development with the Qucs/ADMS "Turn-key" modelling system

- Ques experimental implementation of the BSIM 6.1 MOS transistor model

- Model parameter extraction: linking Qucs with low-cost measurement instrumentation; RF components

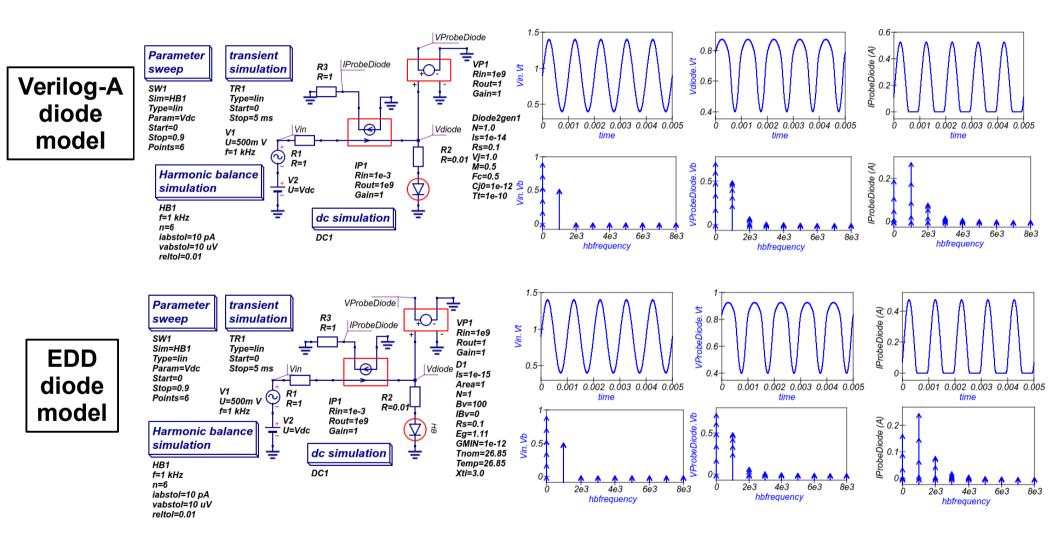

- Ques swept Harmonic Balance simulation: Verilog-A and EDD diode models

- Current and possible future directions for Qucs development

# Ques release 0.0.18: an overview of new simulation and compact device modelling features

Qucs 0.0.18 was released at the end of August 2014. It can be downloaded from the Sourceforge.net web site in binary and source code. The 0.0.18 release is available as binary ready to run code for the Linux (Ubuntu), MAC OSX (Darwin) and Windows (XP, 7, 8 and 8.1) operating systems.

#### **Qucs 0.0.18 Release Notes**

This release brings improvements to many parts of Qucs. The port from Qt3 to Qt4 is still ongoing and many bugs and usability issues have been fixed in the process. A few new features were added and others are in development. See below a short summary of the most noticeable enhancements. Qucs and Qucsator.

- new: Dynamic compilation and loading of Verilog-A modules (beta feature). Addition of a full ADMS/Qucs

"turn key" Verilog-A compact device modelling system to Qucs. Users are no longer required to manually

edit C++ code and the build system to be able to run Verilog-A models. Uses ADMS 2.3.4 (only a subset

of Verilog-A is supported).

- fix: Spice file handling and translator.

- new: Addition of BSIM 3 and BSIM 4 models to Qucs MOS models.

- new: Release of the first model (RFresistor) in a new series of RF models for Harmonic Balance and other forms of Qucs simulation.

- new: HICUM npn and pnp Level 0 V1.3 Verilog-A devices.

- new: HICUM npn level 2 V2.32 Verilog-A device.

#### Qucs 0.0.18 release

### Qucs

- new/fix: Ported several classes from Qt3 Support to Qt4 (work in progress).

- new: use QSettings to store user preferences and application settings.

- new: Copy/duplicate project content files.

- new: Export schematic and diagrams to SVG, PNG, JPG, JPEG, PDF, PDF+Latex, EPS (Inkscape required).

- new: Component library is not included on the Dock Window.

- new: Added checkbox to settings, which allows to load schematics from future versions.

- new: Open Recent menu option.

- new: Set ADMS, ASCO and Octave paths on the application settings.

- new: Use environment variables ADMSXMLBINDIR, ASCOBINDIR, OCTAVEBINDIR to set tools

paths.

- new: Updated translations: pt-BR, pt-PT, ru.

#### **Qucsator**

- new: Refactoring of Quesator namespace. Most of the core functions are under the namespace ques::

- new: Allow to run autotest by adding bugon/assert operator.

- **new:** initial support for unit testing with googletest.

- new: added a Python scripts for parsing Qucs data files.

- **fix:** enable BJT models with (Vtf < 0).

### QucsFilter, QucsAttenuator, QucsHelp, QucsEdit

new/fix: Ported several classes from Qt3Support to Qt4 (work in progress)

### **QucsResCodes**

**new:** QucsResCodes is a program to compute color codes for resistors and resistance values from color codes. The program computes the closest standard resistor value. Users can paste the computed resistor in the schematic.

### Qucs 0.0.18 release

#### **Interfaces**

- Improved Qucs/Octave interface for GUI and Qucssator netlist entry (including a start on a Octave library of plotting functions for Qucs post simulation data visualisation).

- First steps in developing a combined Qucs/Python Qucs simulation capability with high quality date visualisation using matplolib. Applications include basic sensitivity analysis and circuit performance optimisation.

- Preliminary version of Qucs/Octave linked transient simulation capability.

### **Build system**

- Add ADMS as a Git submodule to the Qucs Git repository.

- Added --disable-asco and --disable-adms option to skip the build of included sources.

- Added CMake (experimental) for advanced users building from Git repository.

- OSX: options to build against 10.5 to 10.9 SDK.

- Included packages: ASCO 0.4.9 (patched) and ADMS 2.3.4.

#### **Miscellaneous**

- Project website is now under version control.

- Source code is now under Travis continuous integration service.

- Source code documentation (Doxygen) available on the website.

- Preliminary regression and test suite (qucs-test).

### Bug fixes

Hundreds of bug fixes and code improvements.

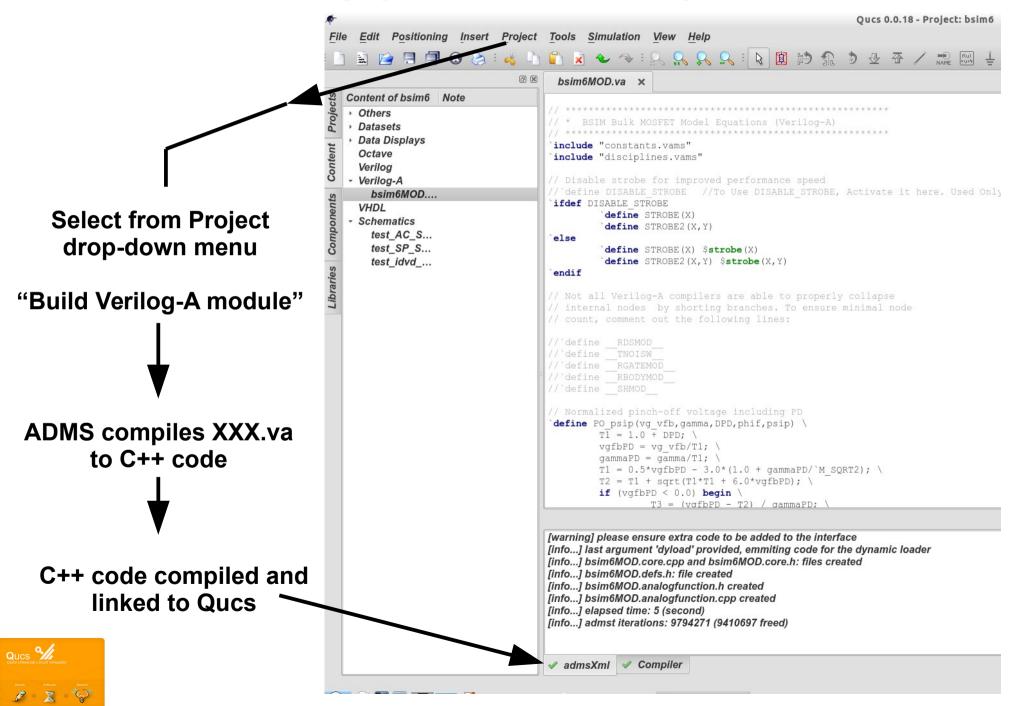

# Compact model development with the Qucs/ADMS "Turn-key" modelling system: 1. Build Verilog-A module

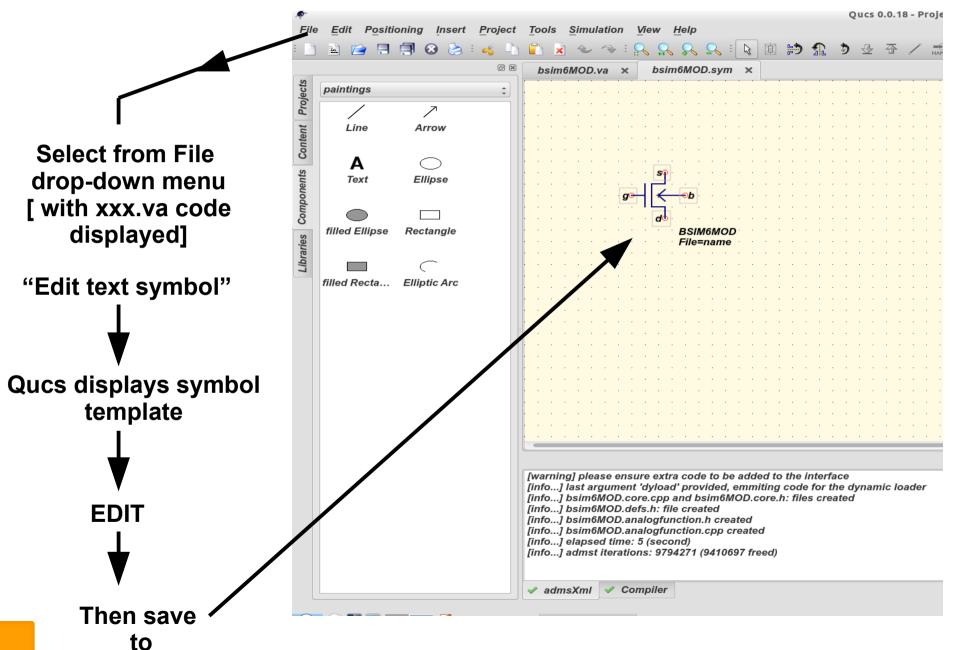

# Compact model development with the Qucs/ADMS "Turn-key" modelling system: 2. Edit text symbol

current project

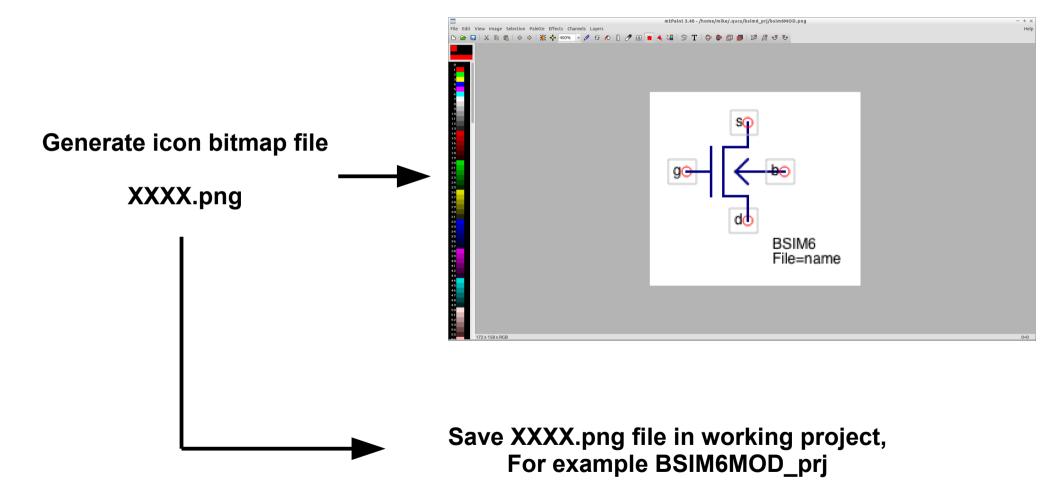

# Compact model development with the Qucs/ADMS "Turn-key" modelling system: 3. Generate and add icon to current project

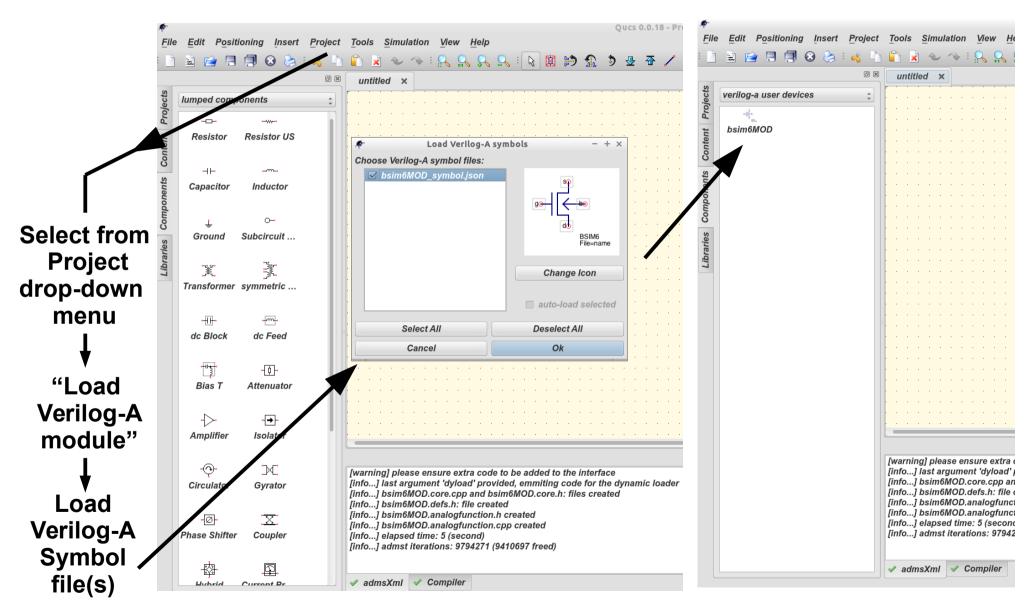

# Compact model development with the Qucs/ADMS "Turn-key" modelling system: 4. Load new model before use

The Qucs Development Team has taken over maintaining the LGPL version of ADMS:

Latest version is ADMS 2.3.4; http://sourceforge.net/projects/mot-adms/

[Includes contributions from Xyce and WRspice ADMS patches]

Source code repository has migrated to: https://github.com/Qucs/ADMS

Download: git clone https://github.com/Qucs/ADMS.git

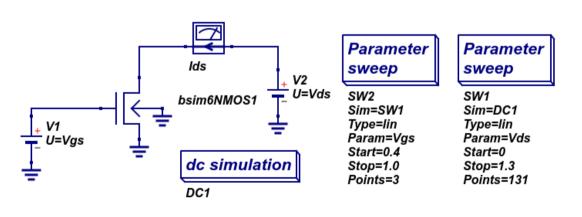

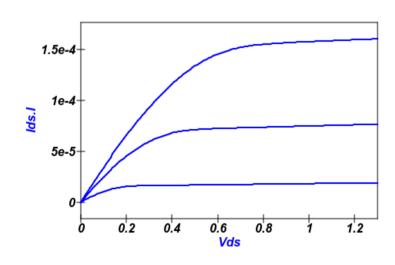

BSIM 6.1 compiles with ADMS 2.3.4 : Roughly 4000 lines of Verilog-A code generates around 27,000 lines of C++ code for compiling and linking to Qucs 0.0.18

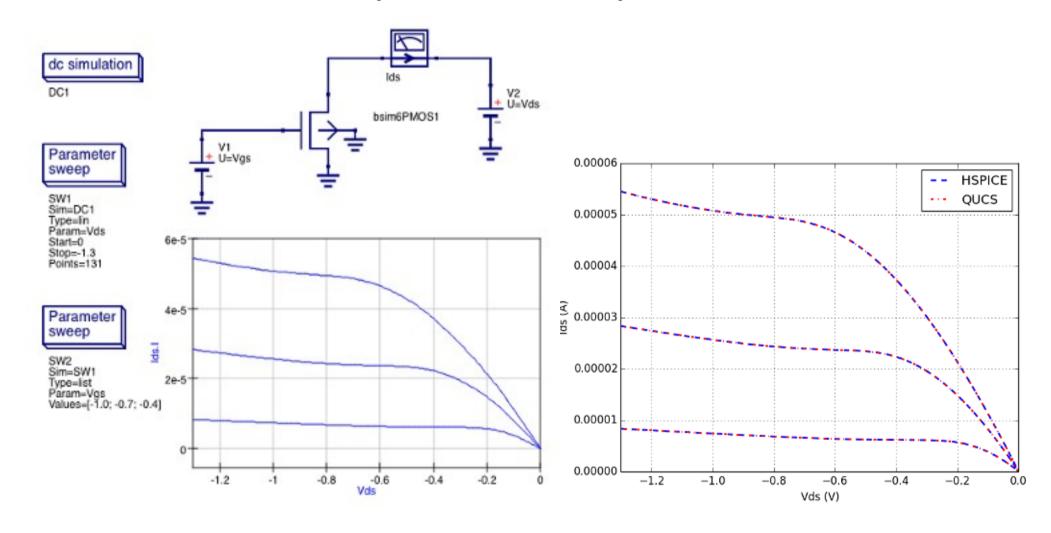

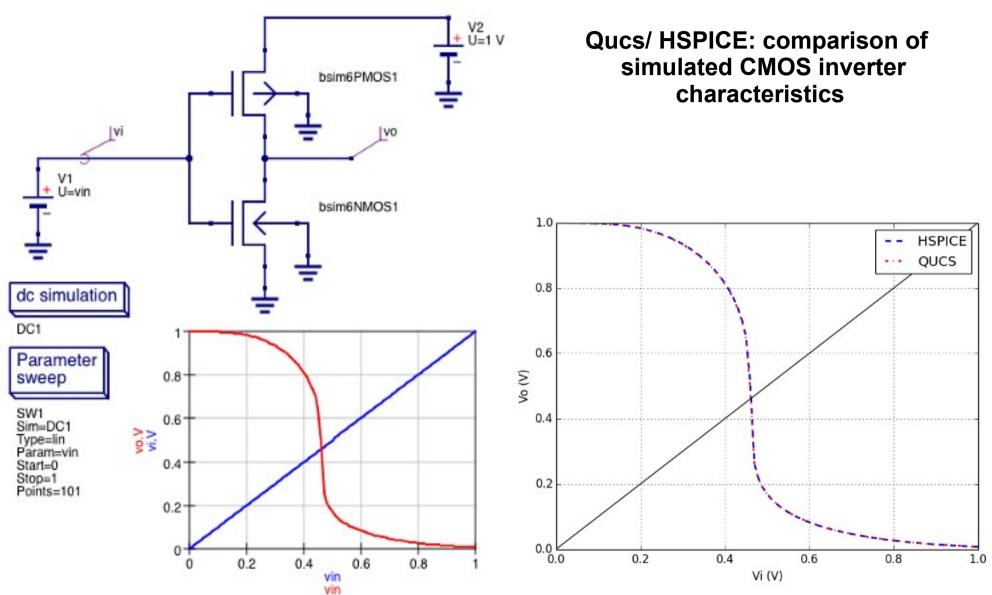

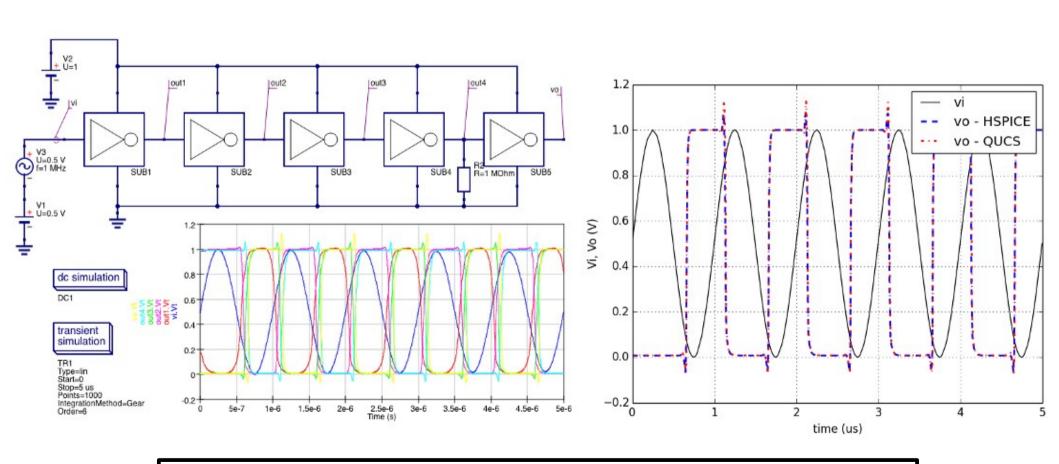

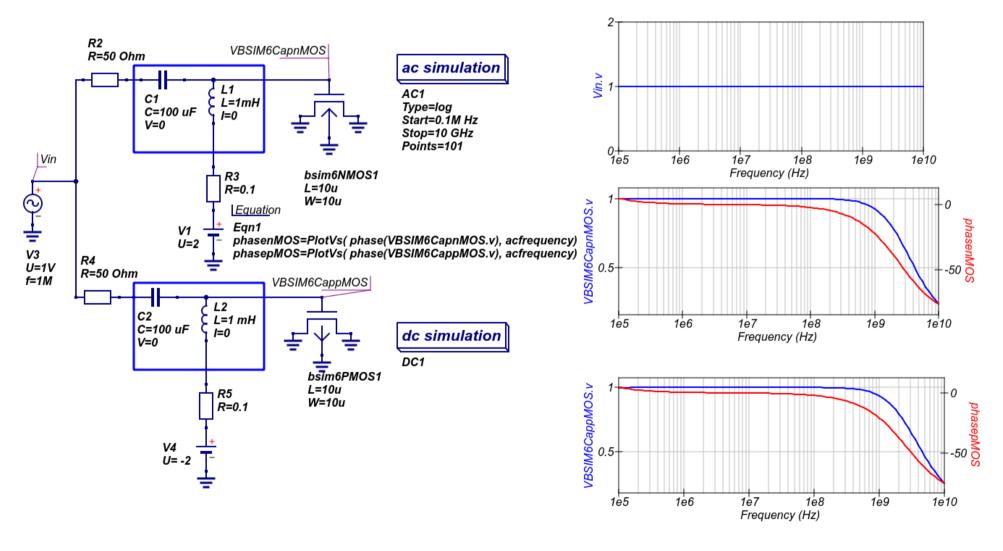

Examples of initial test results for the Qucs version of a BSIM 6.1 MOS n and p devices: the new implementation is currently under test and will be published once the Qucs "Development Team" is satisfied that it functions correctly and accurately. Likely publication will be with the release of the next Qucs snapshot.

acfrequency

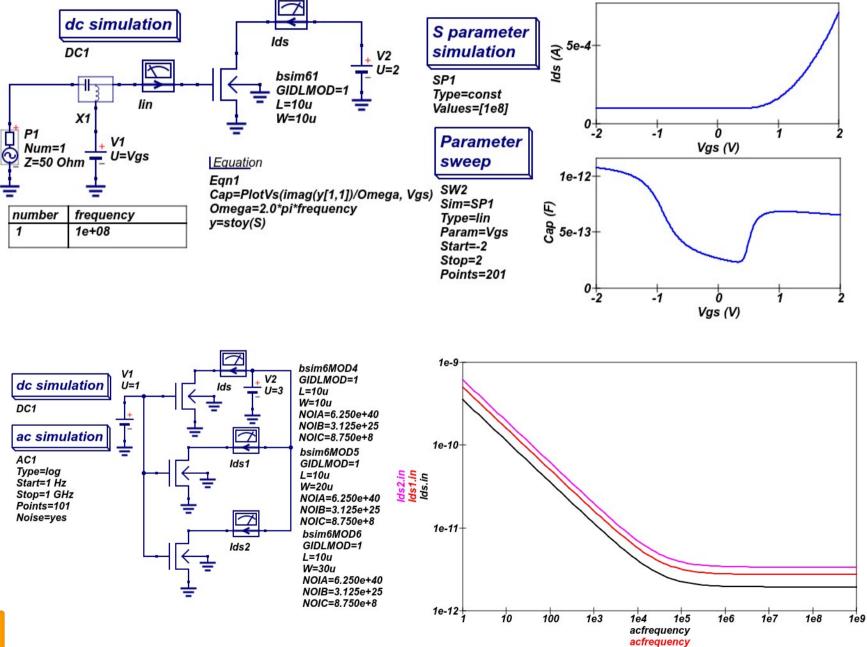

### Qucs/ HSPICE: comparison of simulated nMOS I/V characteristics

### Qucs/ HSPICE: comparison of simulated pMOS I/V characteristics

Qucs/ HSPICE: comparison of simulated CMOS inverter transient characteristics

NOTE: resistor R2 has been added to the original HSPICE test circuit to aid DC convergence.

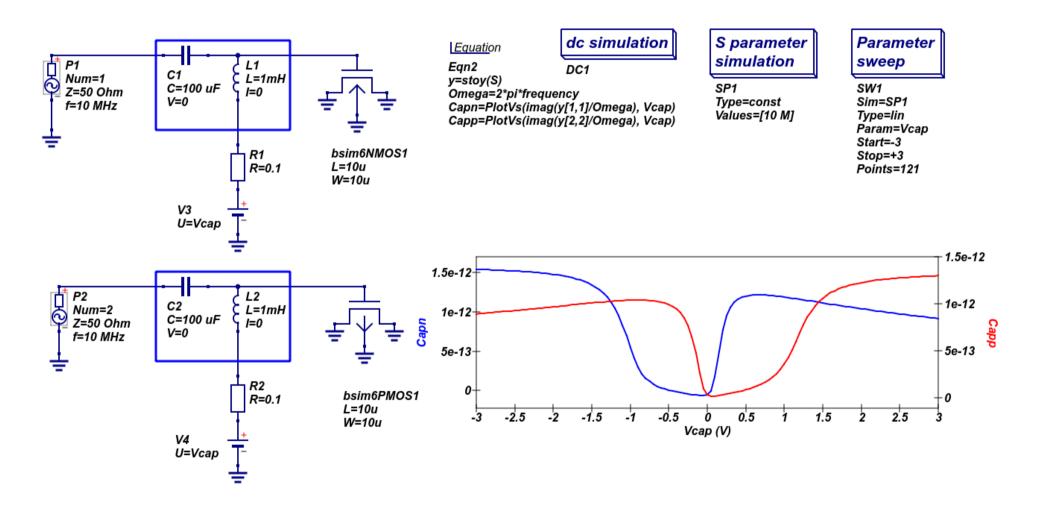

# Ques experimental implementation of the BSIM 6.1 MOS transistor model: more examples; AC small signal simulation

# Ques experimental implementation of the BSIM 6.1 MOS transistor model: more examples; AC small signal S parameter simulation

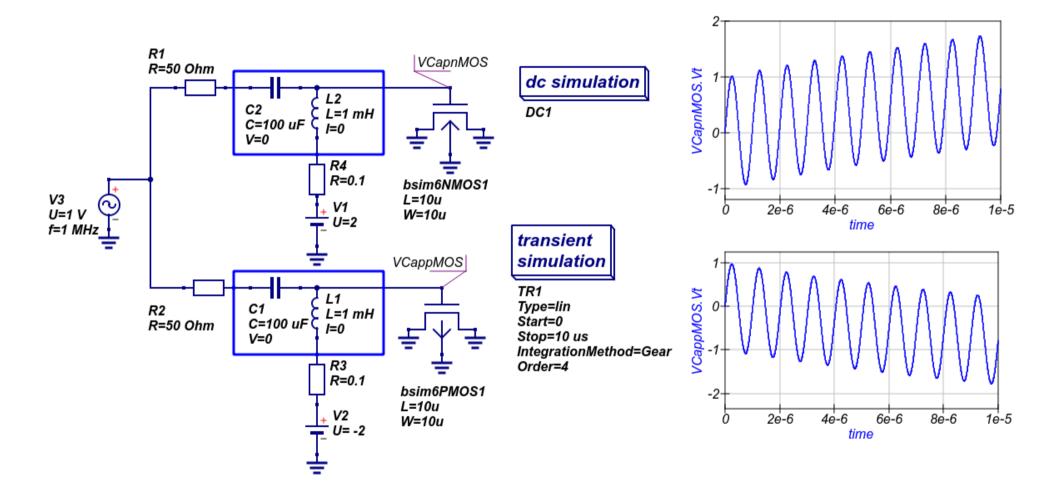

# Ques experimental implementation of the BSIM 6.1 MOS transistor model: more examples; Transient simulation

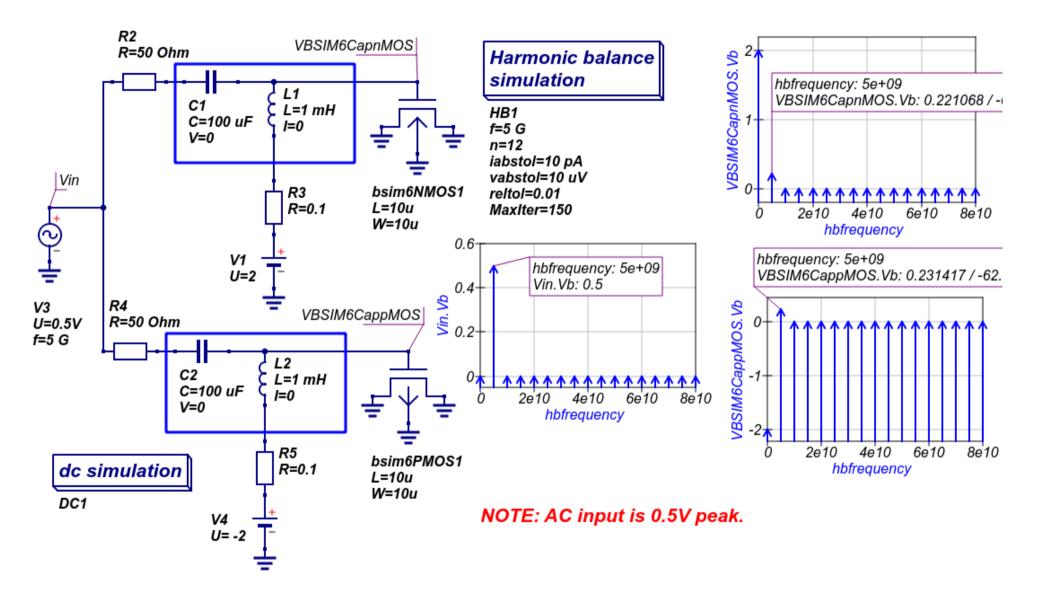

# Ques experimental implementation of the BSIM 6.1 MOS transistor model: more examples; Harmonic Balance simulation

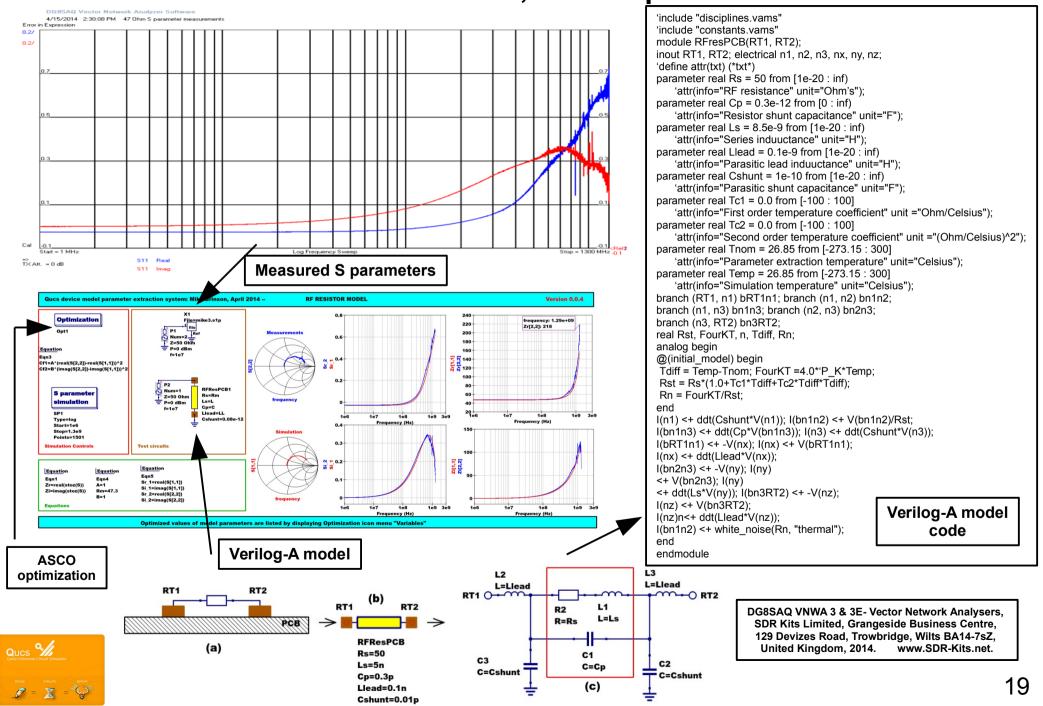

Model parameter extraction: linking Qucs with low-cost measurement instrumentation; RF components

### Ques swept Harmonic Balance simulation: Verilog-A and EDD diode models

### Current and possible future directions for Qucs development

### **Current projects**

- Finish Qt3 to Qt4 port.

- Continue development of the Qucs "Turn-key" Verilog-A modelling system.

- Improve Qucs simulation engines: particularly transient and Harmonic Balance simulation code.

- Improve the Qucs/Octave interface.

- Improve the Qucs/Python interface and continue work on high quality post simulation data visualisation capabilities.

- Add more industrial standard compact semiconductor device models to Qucs.

- Continue development of Qucs RF component models and macromodels.

- Continue work on device model parmeter extraction.

### **Future projects**

- Collect ideas from (1) the Qucs development team and (2) the Qucs user community.

- Update the Qucs project roadmap as a guide to future developments.

- Implement agreed roadmap in a structured way.