# Ques Equation-Defined and Verilog-A RF device models for Harmonic Balance circuit simulation

Mike Brinson

Centre for Communications Technology

London Metropolitan University

UK

Email: mbrin72043@yahoo.co.uk

Vadim Kuznetsov

Bauman Moscow Technical University

Russia

Email: ra3xdh@gmail.com

Abstract—This paper is concerned with the development and evaluation of a number of modelling techniques which improve **Ques Harmonic Balance simulation performance of RF compact** device models. Although Ques supports conventional SPICE semiconductor device models, whose static current/voltage and dynamic charge characteristics exhibit second and higher order derivatives may not be continuous, there is no guarantee that these will function without Harmonic Balance simulation convergence problems. The same comment also applies to a number of legacy compact semiconductor device models. The modelling of semiconductor devices centered on non-linear Equation-Defined Devices and blocks of Verilog-A code, combined with linear components, is introduced. These form a class of compact macromodel that has improved Harmonic Balance simulation performance. To illustrate the presented modelling techniques RF diode and bipolar junction transistor macromodels are described and their Harmonic Balance performance simulated with Ques

Index Terms—Qucs, Xyce, Harmonic Balance RF simulation, compact semiconductor device modelling, equation-defined devices, macromodels.

## I. Introduction

Since the adoption by the Ques circuit simulation community of Equation-Defined Devices (EDD) [1] and Verilog-A analogue modules for compact device modelling [2] they have become amongst the most widely used forms of non-linear device model for established and emerging technologies [3]. The release of the open source General Public License (GPL) "Automatic Device Model Synthesizer" (ADMS) [4], has ensured that Verilog-A will remain one of the dominant compact modelling languages for the foreseeable future. Although ADMS only handles a sub-set of Verilog-A it includes a number of language statements which simplify compact semiconductor device model design [5]. Verilog-A modules and EDD models are now established as important Ques modelling features. Ques treats EDD models and Verilog-A modules as non-linear entities, including those with interface ports linked to internal model nodes via resistors implemented with EDD two terminal branches or Verilog-A code. This structure implies that only non-linear components are connected to internal model nodes. In general, such models function well in the DC, AC and Transient simulation domains without problems. However, the reverse is true with Harmonic Balance (HB) simulation, mainly due to problems occurring when circuits are partitioned

into a frequency domain linear subcircuit and a time domain non-linear subcircuit or because of large changes in device bias points between circuit equation iterative solution steps [6]. Circuit nodes with only non-linear components connected can make partitioning difficult, often resulting in HB simulation non-convergence [6]. A revaluation of the role of EDD and Verilog-A modules suggests that reserving either for the nonlinear sections of an HB model reduces partition failure, provided the remaining model components are linear and at least one linear component is connected to each macromodel node. Moreover, this structure naturally builds into a compact macromodel. Non-linear EDD and Verilog-A modules with current or charge characteristics that have discontinuous differential terms can also be a source of HB simulation non-convergence. This paper introduces EDD and Verilog-A macromodelling techniques which attempt to eliminate the problems found with Ques HB circuit partitioning and device model discontinuities. Semiconductor diode and BJT Qucs HB models are described and their performance simulated with Ques and Xyce(c)[7].

# II. MODELLING A DIODE NON-LINEAR STATIC CURRENT-VOLTAGE CHARACTERISTIC

A basic compact device model for a semiconductor diode is shown in Fig. 1. To prevent HB floating point numerical overflow in the diode forward bias region of operation the Verilog-A function *limexp* is often used to calculate diode current, rather than the standard exponential function exp. When computed diode voltages have a value such that  $\delta \cdot Vd > 80$  function limexp linearizes the diode current characteristic equation in an attempt to prevent numerical overflow. At the crossover point between the diode exponential and linear regions of operation the Id and dId/dVd curves are continuous. Ques C++ code represents real numbers using IEEE binary 64 bit real numbers. These have a decimal range of roughly  $\pm 2.23 \cdot 10^{-308}$  to  $\pm 1.80 \cdot 10^{308}$ . Writing the diode equation given in Fig. 1 in terms of a critical voltage Vcrit, which represents the value of Vd where Id changes from the exponential to the linear region of operation, yields equations 1 and 2 respectively.

$$Id = Is \cdot (exp(\delta \cdot Vd) - 1), \quad \forall (Vd \le Vcrit) \quad (1)$$

$$Id = Is \cdot exp(\delta \cdot Vcrit) \cdot [1 + \delta \cdot (Vd - Vcrit)], \forall (Vd > Vcrit)$$

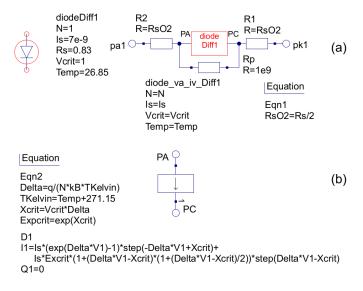

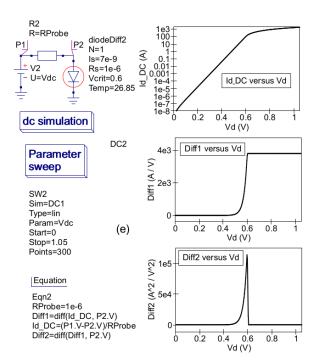

where where  $exp(\delta \cdot Vcrit) >> 1.0$  and  $Vcrit = 308/\delta$ volts. For N=1 and T=300 Kelvin,  $Vcrit(max)\approx 7.7$ volts. Hence with N=1, adopting a value of Vcrit near to, but below 7.7 volts, will ensure that values of Vd below Vcrit do not cause floating point overflow when calculation Id [6]. In the exponential region of operation the first and higher order current derivatives are continuous which is ideal for HB simulation. However, in the linear region of operation (Vd > Vcrit) only the first order derivative is continuous. Figures 2 and 3 introduce a non-linear EDD model and a Verilog-A module which, when either are combined with linear resistors Rs and Rp, form a compact diode macromodel. Typical simulated DC data for a diode macromodel under test are given in Fig. 4. The test circuit has Vcrit = 0.6 volts. This value is set artificially low in order to demonstrate the change from the exponential to the linear region of operation in the diode Id characteristic. In Fig. 4 the plot of  $\frac{d^2Id}{dVd^2}$  against Vd clearly illustrates a discontinuity at Vd = 0.6 volts.

Pa Pk Pa Rs Idiode = Id +Vd/Rp Rp Rp where Id = Is · (Iimexp(

$$\delta$$

· Vd) -1),  $\delta$  = e / (N · K · T) and Iimexp(X) = (X < 80) ? exp(X) : exp(80) · (1-(X-80))

Fig. 1. A semiconductor diode static I/V model: N is the diode emission coefficient, e is the electron charge, K is the Boltzmann constant, T is the diode temperature in Kelvin, Rs is the series bulk and contact resistance and Rp a diode junction parallel leakage resistance.

Fig. 2. A diode compact macromodel: (a) Qucs schematic symbol and macromodel circuit, (b) Qucs EDD diode current I1 selected with function step(). For clarity I1 is displayed on more than one line.

more general equation for the diode model current Id, when

Vd > Vcrit, is given by equation 3.

$$Id = Is \cdot exp(\delta \cdot Vcrit) \cdot \sum_{i=0}^{p} \frac{\delta^{i}}{i!} (Vd - Vcrit)^{i} \quad \forall (Vd > Vcrit)$$

(3)

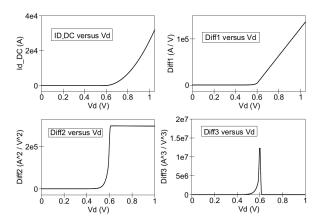

where  $0 \le p \le 5$ . Illustrated in Fig. 5 are a typical set of DC simulation data obtained from the test circuit shown in Fig.4 and a diode model based on the extended macromodel defined by equation 3. In this example both Diff1 and Diff2 are continuous, making the model more suitable for HB simulation.

# III. MODELLING DIODE NON-LINEAR DYNAMIC CHARGE CHARACTERISTICS

Semiconductor diode diffusion and depletion capacitance are given by equations 4, 5 and 6 [11].

$$Cdiff = \frac{dQdiff}{dVd} = Tt \cdot \frac{dId}{dVd} \tag{4}$$

where Tt is the diode transit time in seconds.

$$Cdep = \frac{dQdep}{dVd} = Cj0 \cdot \left[1 - \frac{Vd}{Vj}\right]^{-M} \forall \left(Vd < \frac{Vj}{2}\right)$$

(5)

$$Cdep = 2^{M} \cdot Cj0 \cdot \left[2 \cdot M \cdot \frac{Vd}{Vj} + (1 - M)\right] \forall \left(Vd > = \frac{Vj}{2}\right)$$

(6)

where Cj0 is the zero bias junction capacitance in Farads, M is a pn junction grading coefficient, Vj is the junction potential voltage in Volts, and Qdiff and Qdep are stored diffusion and depletion charges in Coulombs respectively. To reduce the effect of the discontinuity in equation 5 at Vd = Vj the depletion capacitance can be represented by equations 5 and 7.

$$Cdep = 2^{M} \cdot Cj0 \cdot \sum_{i=0}^{p} \frac{(Vd - Vmax)^{i}}{i!}, \forall \left(Vd > = \frac{Vj}{2}\right)$$

(7)

```

// Diode I/V HB model diode_va_iv_Diff1.va

include "disciplines.vams'

'include "constants.vams'

module diode_va_iv_Diff1(pa,pk);

inout pa, pk; electrical pa, pk;

parameter integer N = 1 from [1 : inf);

parameter real is = 1e-14 from [1e-20 : inf);

parameter real Vcrit = 0.6 from (0.4 : 5);

parameter real Temp = 26.85 from [-100 : 200];

parameter real Tnom = 26.85 from [-100 : 200);

real TKelvin, Delta, Xcrit, Expcrit, X;

analog begin

@(initial_model)

beain

TKelvin = Temp+271.15; Delta = `P_Q/(N*`P_K*TKelvin);

Xcrit = Vcrit*Delta; Expcrit = exp(Xcrit);

X = Delta*V(pa, pk);

I(pa,pk) \leftarrow (X \leftarrow Xcrit) ? Is*(exp(X)-1) : Is*Expcrit*(1+(X-Xcrit));

endmodule

```

Fig. 3. Ques diode Verilog-A code: diode current I(pa, pk) selected with ternary operator x?u: z.

Fig. 4. Ques compact diode macromodel test circuit and simulated DC current characteristics:  $Id\_DC = Id$ ,  $Diff1 = \frac{dId}{dVd}$ , and  $Diff2 = \frac{d^2Id}{dVd^2}$ .

Fig. 5. Extended diode compact macromodel simulated DC current characteristics for p=2, Vcrit=0.6~V, Is=7e-9~A,  $Rs=1e-6~\Omega$  and  $T=300~Kelvin:~Id\_DC=Id,~Diff1=\frac{dId}{dVd},~Diff2=\frac{d^2Id}{dVd^2}$  and  $Diff3=\frac{d^3Id}{dVd^3}$ .

where 0 . Although equation 7 gives an approximate value for <math>Cdep at Vd > Vj/2 it is normally acceptable because Cdiff is the dominant capacitive component in this region of diode operation. Setting p=2 and integrating equations 4, 5 and 7 gives

$$Qdiff = Tt \cdot Id \tag{8}$$

$$Qdep = Cj0 \cdot \left(\frac{Vj}{(1-M)}\right) \cdot \left\lceil 1 - \left(1 - \frac{Vd}{Vj}\right)^{1-M} \right\rceil,$$

$$\forall \left(Vd < \frac{Vj}{2}\right)$$

(9)

$$Qdep = 2^{M} \cdot Cj0 \left[ Vdiff + \frac{Vdiff^{2}}{2} + \frac{Vdiff^{3}}{6} \right],$$

$$\forall \left( Vd > = \frac{Vj}{2} \right) \quad (10)$$

where Vdiff = Vd - Vmax and Vmax = Vj/2. A modified EDD macromodel which includes Qdiff and Qdepis shown in Fig. 6. The Verilog-A code for this model is similar to the module code listed in Fig. 3 with I(Pa, Pk) $\leftarrow$  ddt(Q1) added, where Q1 = Qdiff + Qdep. Shown in Fig. 7 is a test circuit for extracting semiconductor diode capacitance from S parameter simulated data. In this circuit the diode under test has series resistance Rs set at  $0.1\mu\Omega$  to ensure that Rs does not affect the accuracy of the extracted values of Cd. The diode under test has DC bias voltage Vdc swept over the range 0 to 0.8 volts and, at each bias point, S[1,1] determined with Ques S parameter simulation. Conversion of S[1,1] to y[1,1] allows diode capacitance values to be extracted from the imaginary component of the y[1,1] data;  $Cd = imag(y[1,1]/(2 \cdot \pi \cdot frequency))$ . Diode parameter  $V_j$  is set at 0.6 volts to be able to observe any discontinuities in the diode capacitance characteristics. Fig. 7 presents plots of Cd, and its first two derivatives, with respect to diode bias voltage Vd. These suggest that the change in depletion capacitance given by equations 5 and 7 is smooth and does not introduce any significant discontinuities in the diode capacitance characteristic.

# IV. HARMONIC BALANCE AND TRANSIENT SIMULATION OF AN RF DIODE DETECTOR

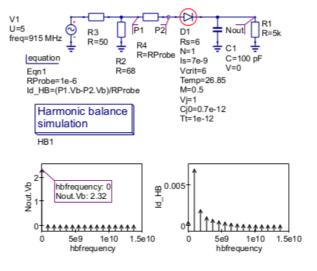

The diagram in Fig. 8 shows an unbiased RF diode detector circuit and a set of Qucs HB simulation output voltage and diode current spectral plots for a 915 MHz five volt peak AC input signal. The detector diode model parameters are similar to the AVAGO HSMS-2820 published SPICE parameters [8].

Fig. 6. A semiconductor diode EDD macromodel including dynamic charge characteristics. For clarity EDD D1 current I1 and charge Q1 are displayed on more than one line

Fig. 7. Diode compact macromodel S parameter simulation: test circuit and Equation scripts for extracting diode capacitance from Qucs S parameter simulated values.

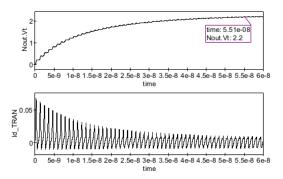

This particular circuit illustrates the performance of the diode HB compact macromodel and how effective HB simulation is in determining the AC steady state response of RF circuits, particularly when compared to number of AC input signal cycles needed before the transient simulation output voltage Nout.Vt approaches a steady state response, see Fig.9.

Fig. 8. RF diode detector test set and HB simulation data plots:  $Is=7e-9A,\,N=1,\,Vj=1.0V,\,Rs=6\Omega,\,Cj0=0.7pF$  and Tt=1e-12s.

Fig. 9. RF diode detector transient simulation data plots: Nout.Vt and  $Id\_TRAN$  against time.

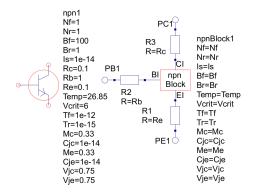

## V. A BJT COMPACT MACROMODEL FOR HB SIMULATION

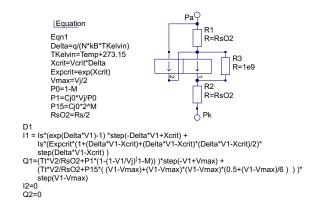

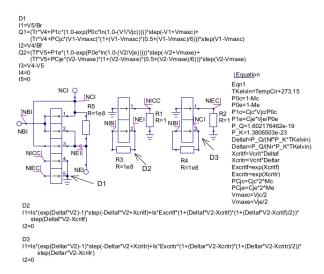

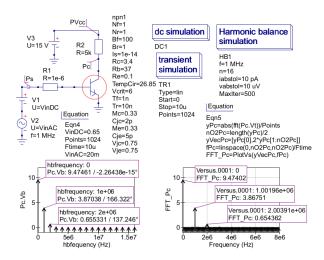

A Ques compact macromodel for an npn BJT modelled by a large signal Ebers-Moll I/V characteristic and nonlinear stored charge is given in Fig. 10. This macromodel is constructed from a nonlinear block called npnBlock and three linear resistors connecting port terminals PC1, PB1 and PE1to npnBlock. Figures 11 and 12 present details of the npn BJT nonlinear static current and dynamic charge properties derived from the semiconductor diode model introduced previously. Figure 13 introduces a basic BJT test bench and a set of Ques HB and transient simulation derived frequency domain spectral plots for the voltage at output node Pc. The latter being obtained with FFT techniques, see Qucs equation Eqn5Fig. 13. DC voltage sources V3 and VinDC were set at 15V and 0.65V to bias the BJT output node Pc at a quiescent DC voltage of approximately 10V at a collector current of 2mA. Comparison of the HB and transient voltage spectral data for node Pc, with VinAC a single tone AC test signal of 1MHz frequency and 20mV peak amplitude, indicates good agreement between both sets of data. The latest development version of Qucs/spice4qucs [9] includes routines for generating Xyce netlists from Qucs schematics. A Xyce netlist for the npnBlock macromodel is given in Fig. 14. This netlist has a similar structure to both the Ques EDD npnBlock model, Fig. 11, and the Verilog-A *npnBlock* module, Fig. 12, introduced previously. However, some minor adjustments were required

Fig. 10. An npn BJT compact macromodel: symbol and circuit.

Fig. 11. A Ques npn BJT EDD macromodel block npnBlock: For clarity EDD D2 and D3 currents (I1) and charge Q1 are displayed on more than one line, BJT current and charge equations are selected with function step().

Fig. 12. A Ques npn BJT Verilog-A code block npnBlock: BJT current and charge equations are selected with ternary operator x?y: z.

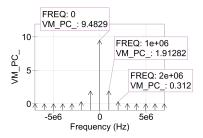

to the Xyce netlist due incompatibilities in some parameter and function names, for example Qucs Temp is replaced by TempCir and Qucs function step() is replaced by Xyce function stp(). Shown in Fig. 15 is the Xyce HB simulation spectral data for the magnitude of the voltage at test circuit node Pc. The date illustrated in Fig. 15 confirms the values

### obtained with Qucs HB simulation.

Fig. 13. A BJT HB and transient simulation test bench: Circuit, node Pc HB simulation data and frequency domain spectral plot of transient simulation data.

Fig. 14. A Xyce npn BJT SPICE subcircuit npnBlock: BJT current and charge equations are selected with function  $stp(\tt)$ .

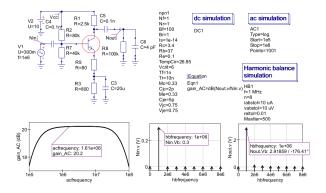

# VI. AC AND HARMONIC BALANCE SIMULATION OF A SINGLE STAGE RF BJT AMPLIFIER

The schematic for a single stage Rf BJT amplifier is illustrated in Fig. 16. This amplifier is designed to give a 20dB voltage gain at midband frequencies. The theoretical midband

Fig. 15. Xyce HB simulation data for the magnitude of node Pc voltage: Test configuration identical to Fig. 13.

magnitude of the amplifier voltage gain is given by equation 11 due to the negative feedback introduced by resistor R9. The Ques plots of small signal AC and HB simulation data show very similar values for the output voltage at node Nout.

$$Vgain \approx 20 \cdot log(R1/R9)$$

(11)

Fig. 16. A 20dB single stage npn transistor RF amplifier: circuit, small signal AC voltage gain and HB simulation data obtained with R9 adjusted to give a gain of 20dB at 1MHz.

### VII. CONCLUSIONS

Harmonic Balance simulation of RF circuits is rarely implemented in GPL circuit simulators derived from Berkeley SPICE 2g6 or 3f5 [10]. Currently, Qucs includes single tone HB simulation. This paper introduces a compact macromodelling approach to Ques HB simulation which is suitable for simulating RF discrete and integrated circuit steady state AC performance The proposed modelling technique introduces a compact macromodelling structure which reduces HB linear and non-linear circuit partitioning problems and helps reduce the effects of discontinuities in model current and charge differential characteristics on HB solution convergence. Experience with the proposed Ques HB compact macromodelling method has shown that it is suitable for any general purpose circuit simulator provided it implements HB simulation and can handle Equation-Defined Devices or Verilog-A analogue modules. HB simulation data for a semiconductor diode and an npn BJT are reported. This data was obtained from test simulations using both the Ques and Xyce GPL simulators.

Good agreement was found between the steady state AC simulation results obtained from Qucs HB simulation and transient time domain simulation.

#### REFERENCES

- S. Jahn, and M. Brinson, "Interactive Compact Modeling Using Ques Equation-Defined Devices", Int. J. Numer. Model. 2008, vol 21, pp. 335-349.

- [2] G. J. Coram, "How to (and How Not to) Write a Compact Model in Verilog-A", IEEE International Behavioural Modeling and Simulation Conference (BMAS), San José, Calfornia, pp. 97-106, October 2004.

- [3] Toshi Lab. (Optical and RF-MEMS Lab), "MEMS DAIQ=MEMS Design and Analysis Interface to Ques", 2011, http://toshi.iis.utokyo.ac.jp/toshilab/?DAIQ [accessed March 2015].

- [4] L. Lemaitre, W. Grabinski and C. McAndrew, "Compact device modeling using Verilog-A and ADMS", Electron Technology Internet Journal, Vol. 35, pp. 1-5, 2003.

- [5] L. Lemaitre, G. J. Coram, C. McAndrew and K. Kundert, "Extensions to Verilog-A to support compact device modeling", IEEE International Behavioral Modeling and Simulation Conference, BMAS-03, pp. 134-138. October 2003.

- [6] S. A. Maas, "Nonlinear Microwave and RF Circuits", Second Edition, Artech House, Boston and London. 2003.

- [7] Sandia National Laboratories, "Xyce Parallel electronic simulator: version 6.2", 2015, https://xyce.sandia.gov/ [accessed March 2015].

- [8] Avago Technologies, "HSMS-282x Surface Mount RF Schottky Barrier Diodes data sheet, Av02-1320EN, May 28, 2009.

- [9] V. Kuznetsov, "QEP: Qucs schematic simulation with ngspice", 2015, https://github.com/Qucs/qucs/wiki/QEP, (also at: https://github.com/ra3xdh/qucs/tree/spice4qucs) [accessed March 2015].

- [10] A.R. Newton, D. O. Pederson, A. Sangiovanni-Vincentelli, "SPICE Version 2g User's Guide", Department of Electrical Engineering and Computer Sciences, University of California: Berkeley, CA. 1981, and B. Johnson, T. Quarles, A.R. Newton, D. O. Pederson, A. Sangiovanni-Vincentelli, "SPICE3 Version 3f User's Manual", Department of Electrical Engineering and Computer Sciences, University of California: Berkeley, CA. 1992.

- [11] P. Anongnetti, and G. Massobrio (Editors), "Semiconductor Devise Modeling with SPICE", McGrew-Hill Inc., New York, 1988.