# **Qucs-S and QucsStudio for Compact Device Modeling**

# Mike Brinson Centre for Telecommunications Research London Metropolitan University, UK brinsonm@staff.londonmet.ac.uk

September 14-18, 2020

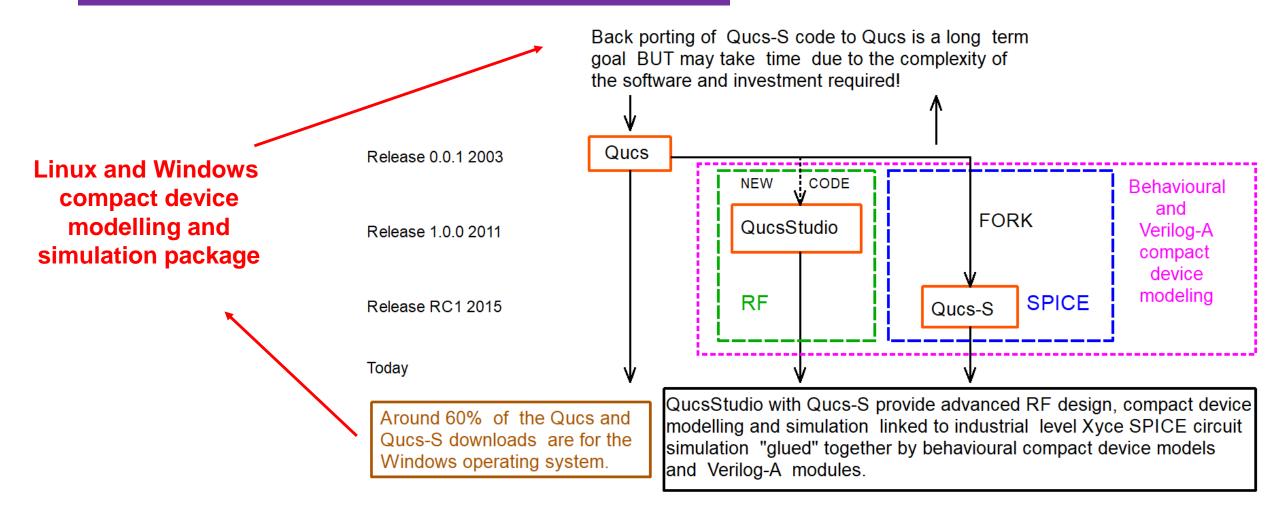

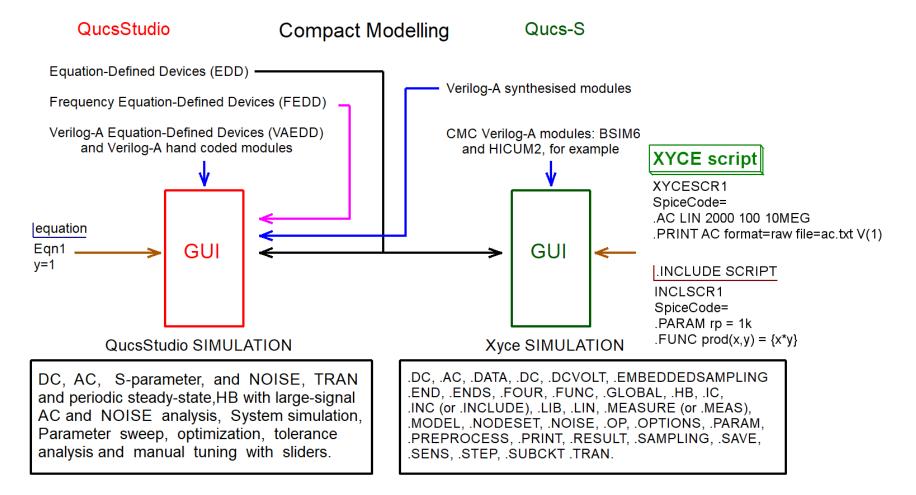

- Qucs-S and QucsStudio compact device modelling and simulation features

- QucsStudio and Qucs-S: a combined modelling and simulation package

- QucsStudio Verilog-A module development: facilities and properties

- Built in Verilog-A modules: CMC and others

- Equation-Defined Device (EDD) modelling: principles and application

- Qucs-S Verilog-A module synthesis: facilities and link to QucsStudio

- <sup>D</sup> The Verilog-A Equation-Defined Device (VAEDD): structure and properties

- Enhanced QucsStudio compact device modelling and simulation

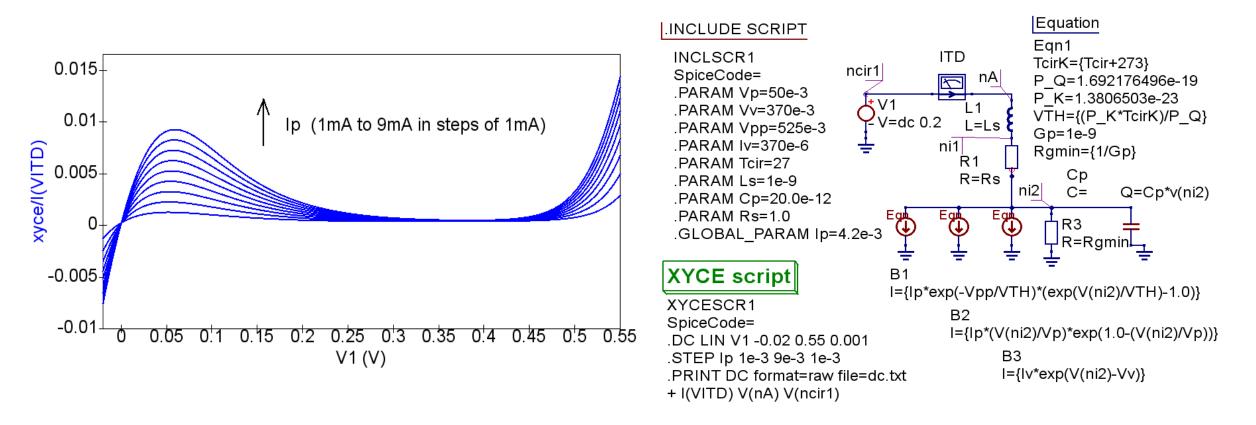

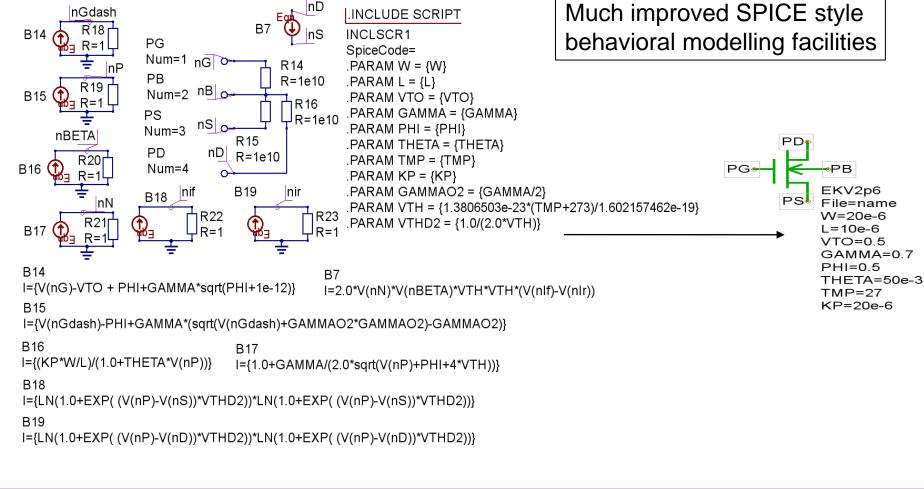

- Enhanced Qucs-S/Xyce behavioural EDD modelling

- $\hfill\square$  Onwards to the next generation package

QucsStudio and Qucs-S

Verilog-A Development

|                                     | 8 🗞 🖓 🗋 🖹 🗙 👻 🍡 🔒 🤱 Ձ 乌 🔒 💥 📂 א א א א א א א א א א א א א א א א א א                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Synthesize                                                                                                                             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Edit<br>Verilog-A<br>module<br>code | <pre>22207 Note<br/>1// Verilog-A B: module code: Template.va<br/>2 'include "constants.vane"<br/>4<br/>5// Module name becomes name of the model file n<br/>6 module Transistor (externalBase, Collector, Emil<br/>6 module Transistor (externalBase, Collector, Emil<br/>7 inout externalBase, Collector, Emil<br/>9 electrical Base;<br/>10 'define attr(txt) (*txt*)<br/>11 'define GMIN le-10<br/>12<br/>13 parameter real Bf=100 from [1:inf] 'attr(in<br/>14 parameter real Bf=100 from [0:inf] 'attr(in<br/>15 parameter real Varanyo from [0:inf] 'attr(in<br/>16 parameter real Varanyo from [0:inf] 'attr(in<br/>17 parameter real Colo from [0:inf] 'attr(in<br/>19 parameter real Module Colo from [0:inf] 'attr(in<br/>20 parameter real Mi=0.33 from [0:inf] 'attr(in<br/>20 parameter real Mi=0.33 from [0:inf] 'attr(info-filecker noise coefficient unit="1");<br/>22 parameter real Kf=10- from [0:inf] 'attr(info-filecker noise current exponent" unit="1");<br/>23 parameter real Af=0 from [0:inf] 'attr(info-filecker noise current exponent" unit="1");<br/>24 parameter real Af=0 from [0:inf] 'attr(info-filecker noise frequency exponent" unit="1");<br/>25 parameter real Af=0 from [0:inf] 'attr(info-filecker noise frequency exponent" unit="1");<br/>26 c<br/>27 real Tj, Vtemp, Vbc, Vcc, Ibe, Ibc, Ire, Qbe;<br/>28</pre> | Verilog-A<br>Module<br>Code<br>[with ADMS]<br>To form<br>"Transistor.va.cpp"<br>and Compile<br>C++ code<br>to form<br>"Transistor.dll" |

Verilog-A Development

| Schematics                                                                       | 020' Note                      |                              |                                       | X1<br>Bf=Bf                                                    | 🔊 Edit (     | Compon            | ent Properties | · · · · · · · · · · · · · · · · · · ·                             | ? >              | <pre></pre>                           |

|----------------------------------------------------------------------------------|--------------------------------|------------------------------|---------------------------------------|----------------------------------------------------------------|--------------|-------------------|----------------|-------------------------------------------------------------------|------------------|---------------------------------------|

| MOSAKFig3B.sch<br>MOSAKS2020Fig1.sch<br>MOSAKS2020Fig2.sch<br>MOSAKS2020Fig3.sch |                                |                              | Rbase=Rbase<br>Is=Is<br>Vearly=Vearly | user compiled model Name: X1 ✓ display in schematic Properties |              |                   |                |                                                                   | dic              |                                       |

| MOSAKS2020Fig3A.sch<br>RCpcb1.sch<br>nBJT.sch                                    | 3-рог                          | o <u>externalBas</u> ∉<br>PB |                                       | Cj0=Cj0<br>Vj0=Vj0<br>Fc=Fc<br>Mj=Mj                           | show         | Name<br>File      |                | Description<br>name of source fi                                  | ile              |                                       |

| ĕ testBJTnpn.sch<br>✓ Verilog<br>MOSAK2020Fig3.va                                |                                | o - Emitter<br>PE            |                                       | Temp=Temp<br>Kf=Kf                                             | V V<br>V     | Bf<br>Rbase<br>Is | Rbase          | forward current g<br>base resistance<br>saturation current        |                  |                                       |

| MOSAK2020Fig3B.v<br>Transistor.va                                                | Drag and drop                  | Rbase=                       | npn1                                  | Af=Af<br>Ffe=Ffe                                               | $\checkmark$ | Vearly            | Vearly         | early voltage<br>zero-bias depletic                               |                  |                                       |

| Octave<br>> C++ Sources<br>> Data Displays                                       | "transistor.va"                |                              | ls=1.0e-16<br>Rbase=1.0               |                                                                |              | Fc                | Fc             | junction built-in p<br>depletion capacit<br>junction exponen      | ance coefficient |                                       |

| <ul> <li>PCB Layouts</li> <li>Datasets</li> <li>Others</li> </ul>                |                                |                              | Ffe=1.0<br>Af=0.0<br>Kf=1e-9          | · · · · · · · · · · · · · · · · · · ·                          | y<br>y       | Temp<br>Kf        | Temp           | simulation tempe<br>flicker noise coeff                           | rature           |                                       |

| Otters                                                                           |                                |                              | Temp=26.85<br>Mj=0.33<br>Fc=0.5       | · · · · · · · · · · · · · · · · · · ·                          |              |                   | Ffe            | flicker noise curre<br>flicker noise frequ<br>transistor type [n] | iency exponent   | · · · · · · · · · · · · · · · · · · · |

|                                                                                  |                                |                              | Vj0=0.75<br>Cj0=1.0p<br>Vearly=100.0  | · · · · · · · · · · · · · · · · · · ·                          |              | Type              | וואוו          | 71 - 1                                                            | Edit Browse      |                                       |

|                                                                                  | Add pins PC,PI<br>Draw model s |                              |                                       | · · · · · · · · · · · · · · · · · · ·                          |              | OK                |                | Apply                                                             | Cancel           |                                       |

Pass symbol parameter values to "user compiled model" via name = name construction.

Built in Verilog-A modules

Windows "turn key" ADMS Verilog-A module development system

QucsStudio Standard SPICE models: Diode, BJT, MOSFET, JFET and MESFET

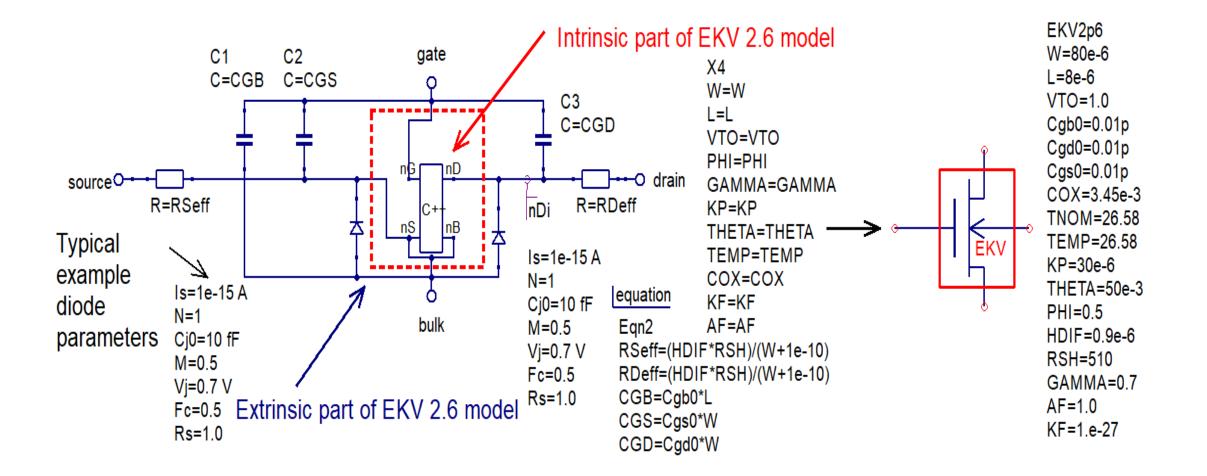

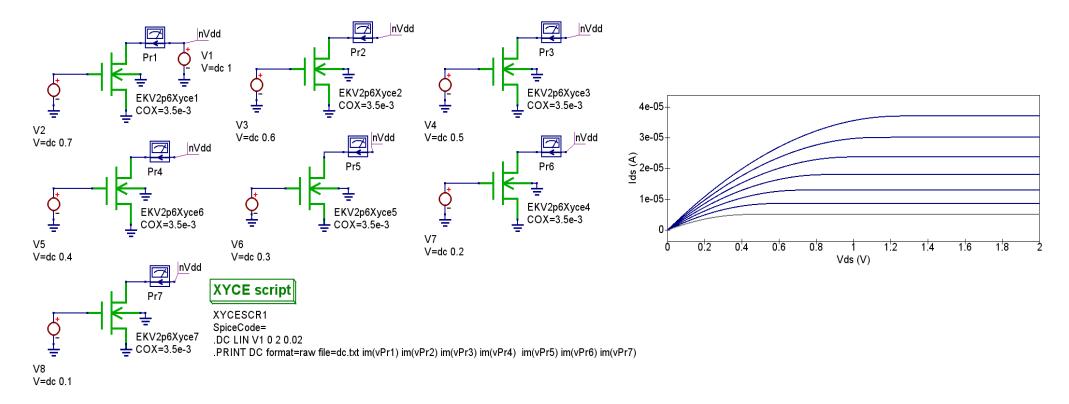

CMC and other models: BJT – HICUM/L2/L0 MOSFET – EKV2.6 The Windows serial (single processor) version of Xyce is compiled under Cygwin64 using static libraries. Hence, a "turn key" Verilog-A module development system is NOT implemented.

Qucs-S/Xyce Standard SPICE models: Diode, BJT, MOSFET, JFET and MESFET CMC and other models: BJT – VBIC 1.3, FBH HBT\_X, HICUML0/L2, MEXTRAM. MOSFET – BSIM3, BSIM4, BSIM6, BSIM\_SOI,

BSIM\_CMG, MVS, PSP

Verilog-A ADMS generated models

CMC = Compact Modelling Coalition

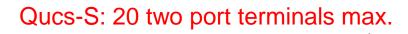

QucsStudio: 8 two port Terminals max.

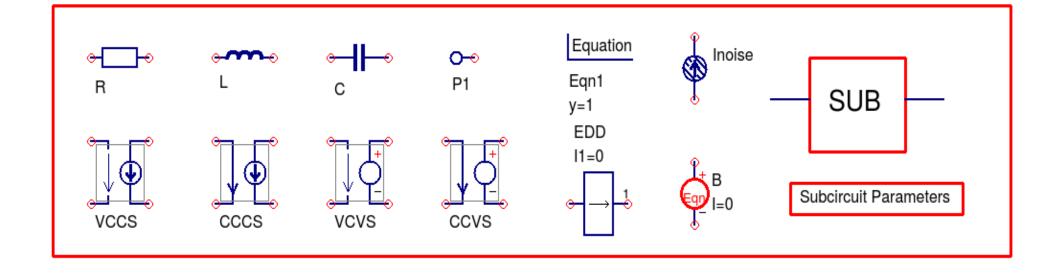

**Equation-Defined Devices**

I = I(V), g = dI/dV Q = Q(V,I), C = dQ/dV =  $\partial Q(V)/\partial V + \partial Q(I)/\partial I \cdot g$ , where the current flowing in branch n is I<sub>n</sub> = I(V<sub>n</sub>) + d/dt(Q<sub>n</sub>), and 1 <= n <= 20.

• EDD is a multiterminal nonlinear component with branch currents that can be functions of EDD branch voltage, and stored charge that can be a function of both EDD branch voltages and currents

- EDD is similar, but more advanced to the SPICE 3f5 B type I or V controlled sources

- EDD can be combined with conventional circuit components and Qucs-S equation blocks when constructing compact device models and subcircuit macromodels

- EDD is an advanced component, allowing users to construct prototype experimental models from a set of equations derived from physical device properties

- EDD operator d/dt is undertaken internally by Qucs-S

- Qucs-S EDD can have a maximum of 20 two terminal branches

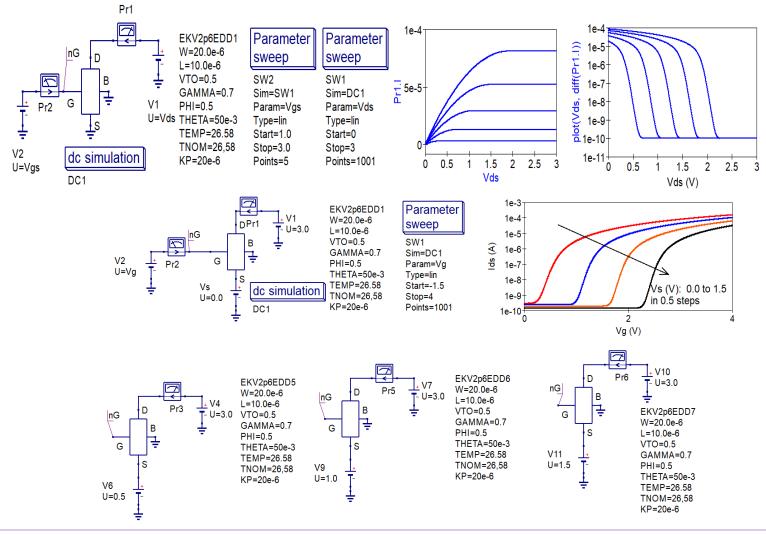

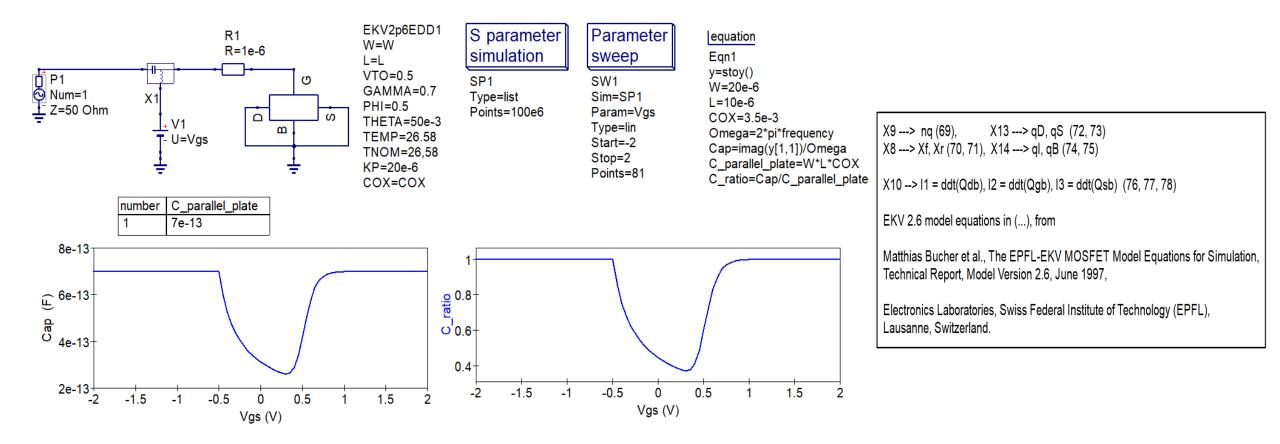

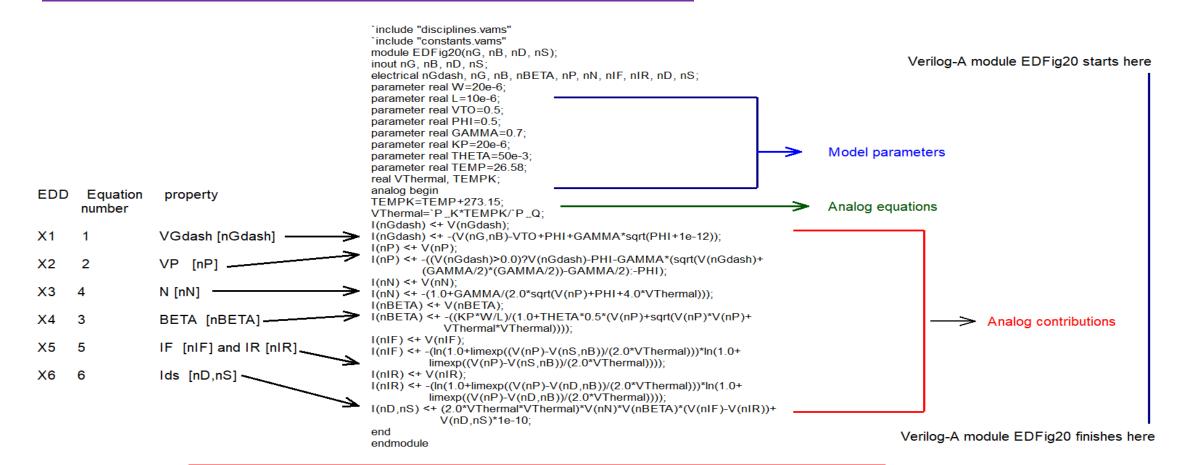

#### X5 X1 X6 I1=In(1.0+limexp((\_v3-\_v5)/(2.0\*VT))\*In(1.0+limexp((\_v3-\_v5)/(2.0\*VT)) 11= v2-VTO+PHI+GAMMA\*sqrt(PHI+1e-12) l1=(2.0\*VT\*VT)\*\_v5\*\_v4\*(\_v3-\_v2) + \_v1\*1e-10 12=ln(1.0+limexp((\_v3-\_v4)/(2.0\*VT))\*ln(1.0+limexp((\_v3-\_v4)/(2.0\*VT)) ÷ nBETA nIF nIR PGO-PDOnD nD nG nGdash ÷ nin\_statc PSO-Т PB O + + + ns R1 + + + + ÷ I1=f(\_v1, \_v2) R=1 on ja nS 支 6. Q1=0 늧 12=0 nIR Q2=0 nout\_static R5 R6 ÷ ÷ nP ÷ R=1 R=1 ÷ R=1 5. Ţ R3 nGdash ÷ nBETA UR=1 V(nin...static) = X7:...v2 R= Χ4 X3 11=(KP\*W/L)/(1.0+THETA\* v2) $V(nout\_static) = X7:II(\_v1,\_v2)$ I1=1.0+GAMMA/(2.0\*sqrt( v2+PHI+4.0\*VT) R2 R=1 equation HEqn1 TEMPK=TEMP+273.15 11=if( v2 > 0.0, v2-PHI-GAMMA\*(sqrt( v2+(GAMMA/2)\*(GAMMA/2)) -GAMMA/2), -P VT=1.3806503e-23\*TEMPK/1.602175462e-19 1. VG'=VGdash = VG-VTO+ $\Phi$ + $\beta$ · sqrt( $\Phi$ ) 2. VP=VG'- $\Phi$ - $\gamma$ · (sqrt(VG'+( $\gamma/2$ )<sup>2</sup>) - $\gamma/2$ ) EKV2p6EDD1 3. BETA = $(KP \cdot W/L)/(1.0 + \theta \cdot VP)$ W=20.0e-6 L=10.0e-6 4. N=1.0 + $y/(2.0 \cdot \text{sqrt}(VP+\theta+4.0 \cdot VT))$ VTO=0.5 GAMMA=0.7 5. $IF = ln(1.0 + limexp(X1/2) \cdot ln(1.0 + limexp(X1/2))$ G PHI=0.5 THETA=50e-3 $IR=In(1.0+Iimexp(X2/2) \cdot In(1.0+Iimexp(X2/2))$ TEMP=26.58 X1=(VP-VS)/VT, X2=(VP-VD)/VT TNOM=26,58 KP=20e-6 6. IDS=2.0 $\cdot$ N $\cdot$ $\beta$ $\cdot$ VT<sup>2</sup> $\cdot$ (IF-IR) EKV 2.6 long channel static I/V model equations EKV 2.6 intrinsic long channel model symbol

leti

<u>ceatech</u>

life.augmented

Mike Brinson

GRENOBLE 2020

SSCIRC

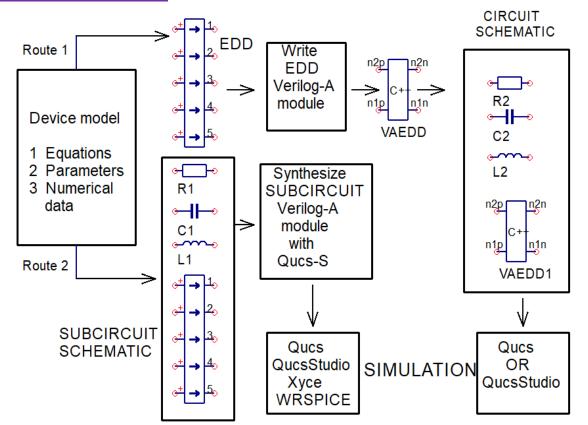

Qucs-0.0.22-S includes a GPL Verilog-A synthesis tool for compact device modeling.

- The Verilog-A synthesizer is a fully working version of this open source ECAD tool,

- Verilog-A device/subcircuit models can be synthesized from the following built in components:

GRENOBLE

#### 🛷 Qucs 0.0.21 - Project: EKV2.6Xyce

File Edit Positioning Insert Project Tools Simulation View Help

| <ul> <li>□ ■ □ ■ ■ ■ ■ ● ● ● ●</li> <li>■ ■ ■ ■ ■ ● ●</li> <li>■ ■ ■ ■ ●</li> <li>■ ■</li> <li></li></ul> | Text Editor       Ctrl+1         Filter synthesis       Ctrl+2         Active filter synthesis       Ctrl+3 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Store Content of EKV2.6Xyce Note<br>Datasets<br>Data Displays<br>Verilog<br>Verilog-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Line calculationCtrl+4Component LibraryCtrl+5Attenuator synthesisCtrl+7Resistor color codesCtrl+8           |

| ♥ VHDL<br>Octave<br>Schematics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Compact modelling   Build Verilog-A module from subcircuit Build XSPICE IFS file from subcircuit            |

| studio<br>EKV2P6No1.sch 4-port<br>EKV2P6No1A.sch 4-port<br>test DCEKV2p6No1.sch<br>XSPICE<br>Others                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EKV2p61<br>W=20e-6<br>L=10e-6<br>VTO=0.5<br>GAMMA=0.7<br>PHI=0.5<br>THETA=50e-3<br>TMP=27<br>KP=20e-6       |

Internal nodes - two I(xx) <+ ... contributions per EDD equation External nodes- one I(yy) <+ ... contribution per node pair.

Mike Brinson

Centech Grenoble

soitec UGA Verilog-A module synthesis

GRENOBLE 2020

ESS

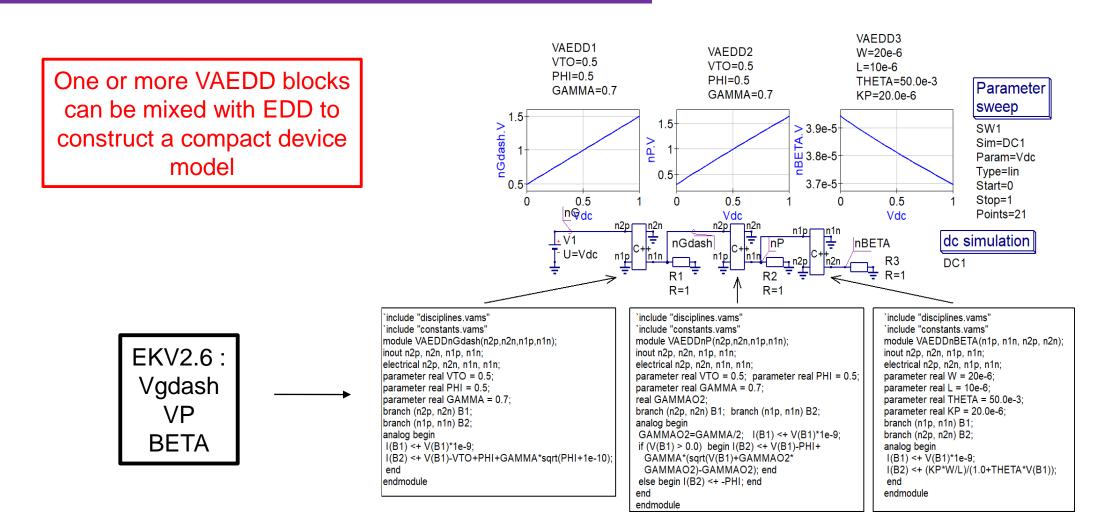

soitec UGA Verilog-A Equation-Defined Devices

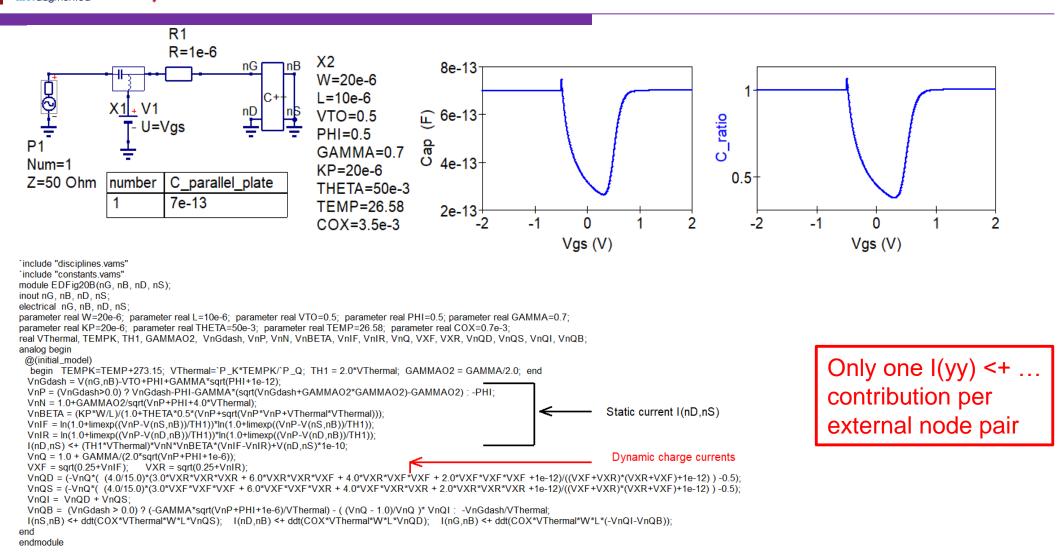

Simulation of complex EDD compact models can be very slow.

leti

Ceatech

- Constructing complex Verilog-A models often requires considerable time and effort.

- Introduce a compromise: construct a compact device model from a mixture of EDD blocks and very simple Verilog-A modules where each Verilog-A module models at most two or three EDD equations.

#### These simplified Verilog-A blocks are called Verilog-A Equation-Defined devices or VAEDD

**VAEDD** Example

QucsStudio 3.3.2

QucsStudio 3.3.2 was released on the 15 July 2020 two years after version 2.5.7.

### New features: NOT in any specific order

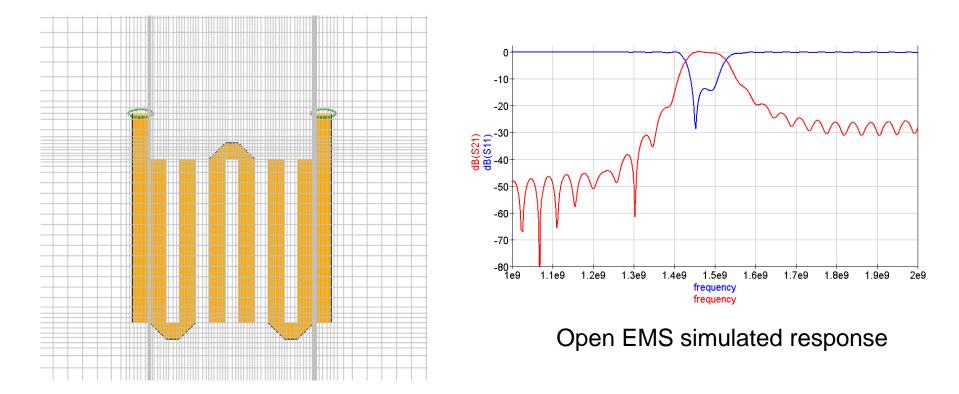

□ EM field simulation using openEMS,

- □ New diagram: equation,

- □ HICUM L0 model implemented,

- □ Improved random-number generation,

- □ Smith chart: enable impedance and admittance circles,

- □ New document type: PCB layout,

- □ Differentiate name.i and name.v in simulator equations,

- □ Complex source and load impedance possible in matching dialogue.

## Plus others and many bug fixes

UGA Enhanced QucsStudio features

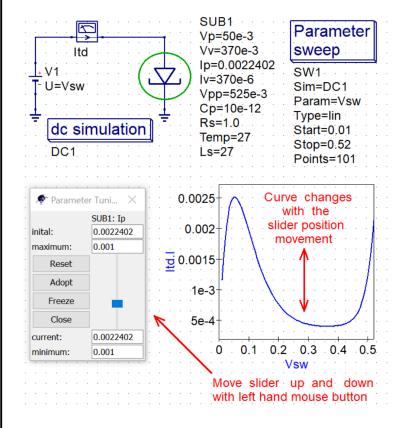

This package has reached an advanced stage of development in that it offers an almost complete set of circuit simulation routines covering the d.c. to transient domains with significant additions beyond SPICE 3f5, like multitone Harmonic Balance analysis, Monte Carlo analysis, parameter sweep, multi-port S parameter and noise simulation, optimization and system simulation.

scitec

- Full "turn-key" Verilog-A compact modelling is also offered via the ADMS software.

- In terms of development QucsStudio is particularly interesting in that it is the first of the Qucs series of circuit simulators to introduce interactive animation as a tool for advanced circuit simulation.

- QucsStudio allows one or more parameter values to be simultaneously controlled by sliders.

- With the computational power of a modern PC changes in simulation output data can be observed as movements in plotted curves as the sliders are moved.

leti

Ceatech

Measurements: **Digilent "Analog** Discovery 2" [16]

A simple RC low pass passive filter example showing an advanced test bench schematic with a computer controlled transfer function measurement system where the measured output data is converted from CSV format to **Qucs simulation control ICONS.**

🔊 Parameter Tuning R and C equency (Hz), V(nCH1) (dB), V(nCH2) (dB) 0.002475259479034487 \_0.05342483298879909 C1: C R1: R 9234826 0.002737357565619841 -0.06 **Parameter** 2261.6 3.912e-06 inital: tuning 6784.8 1.1736e-05 maximum: Reset 4803322 0.002665367428724274 49814920499545\_0\_002773494133118848\_\_0\_772140532471802 61914688960386, 0.00247947778989356, -1.06731010541293 Adopt Freeze 000 .0.05769952830801026 -58.318552606 Close current: 1669.06 3.90809e-06 Octave script to convert XXXX CSV data to simulation control lists 226.16 3.912e-07 minimum: ac simulation Synthesized simulation AC1 Type=list Points=2:2.4045:2.8909:3 9 621 95 726 115 09 138 3 a.c. control lcon and equation Eqn2 measured data lcons V nCH1=[0 026235,0.0024625,0.0025311,0.0025938,0.0026833,0.0027652,0.0026654,0.0027735,0.0024795,0.0022577,0.0024353,0.0023488,0.00236 equation Eqn3 V\_nCH2=[-0.053425,-0.066916,-0.085804,-0.11294,-0.15182,-0.20755,-0.28677,-0.39858,-0.55554,-0.77214,-1.0673,-1.4611,-1.9741,-2.6216,-3.4144,-4.3522,-5.4268,-6.6212,-7.9 Measured data and R=1669.06 TC=3.90809e-06 simulation output visualization Ean1 dBVnCH1=dB(nCH1.v) dbVnCH2=dB(nCH2

10

100

Frequency (Hz)

1e3

1e4 3e4

Measured RC data in CSV format

soitec UGA Enhanced QuesStudio features

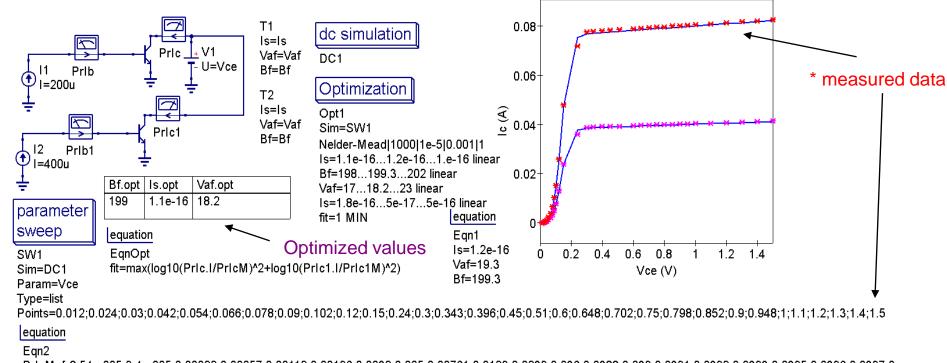

PricM=[-8.54e-005,9.4e-005,0.00022,0.00057,0.00112,0.00196,0.0032,0.005,0.00761,0.0129,0.0239,0.036,0.0388,0.039,0.0391,0.0392,0.0393,0.0395,0.0396,0.0397,0 lequation

#### Eqn3

leti

Pric1M=[-0.00017,-1.31e-005,0.00044,0.0011,0.00224,0.00363,0.0064,0.0101,0.0152,0.0258,0.0478,0.0719,0.0776,0.0779,0.0782,0.0783,0.0785,0.0789,0.0791,0.0793,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0789,0.0791,0.0793,0.0785,0.0783,0.0785,0.0789,0.0791,0.0793,0.0785,0.0785,0.0789,0.0791,0.0793,0.0785,0.0785,0.0789,0.0791,0.0793,0.0785,0.0785,0.0785,0.0789,0.0791,0.0793,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785,0.0785

Three parameter optimization (Bf, Is, Vaf) with parallel IC/Vce BJT test bench using a single Vce parameter sweep and (1) Ib=200u, PricM measured Ic data and (2) Ib= 400u, Pric1M measured Ic data.

EM field simulation using openEMS: 1.5 GHz bandpass filter (imported from HyperLynx file by Koen De Vleeschauwer). Example developed by Dr M. Margraf as part of the Qucs-Studio 3.3.2 release.

#### Xyce 7.1 was released on 8 June 2020. New features: NOT in any specific order

- Non-linear solution dependent capacitors Cap1 1 2 q= {ca\*(c1\*v1\*ln(cosh((v(1,2)-v0)/v1)+c0\*v(1,2))}, or Cap1 1 2 c= {ca\*(c0+c1\*tanh((v(1,2)-v0)/v1))}, where both forms are implemented to ensure charge conservation,

- C-style ternary conditional operator,

- .LIN transfer analysis and extraction of S, Y and Z parameters from a general multiport network,

- .SAMPLING : calculates a full analysis (.DC, .TRAN, .AC etc.) over a distribution of parameter values,

- Sweep loops can now use .DATA command

### Plus others and many bug fixes

# A Xyce SPICE style tunnel diode compact model with a test bench for investigating the effects of stepped device parameters

nGdash

INCLUDE SCRIPT

nD

Ids versus Vds output characteristics generated by .DC scan using parallel test circuits with fixed values of Vgs

- Xyce 7.0/7.1 and beyond: Improved mixed-signal interface via the Verilog Procedural Interface (VPI); Increased Verilog-A simulation speeds; bug fixes (.MEASURE, .AC etc); Improved simulation data output. Current and future Verilog-A developments: Xyce/ADMS compiler modified to use analytic derivatives, new Xyce XML templates. Possible future Verilog-A additions – full implementation of ddx function and a new non-ADMS-based model compiler !.

- Tighter linking between QucsStudio/Qucs-S, Verilog-A/Xyce and device/circuit parameter measurements via an Octave "Toolkit".

- Introduction of multi-physics modelling via links to OPENMODELLICA: simulation of real world systems built from non-electrical and electrical components.

- Low-cost high-performance PC engineering workstations have encouraged the development of compact device modelling and circuit simulation tools centered on a high-resolution graphics interface for schematic drawing, simulation control and output data visualization. This presentation outlined the capabilities of the Qucs/Qucs-S and QucsStudio series of circuit simulators and modelling tools.

- These tools allow interactive prototyping of compact device models and their testing using Qucs/QucsStudio and Qucs-S as a central platform in the construction of Verilog-A modules and Equation-Defined Device models.

- Each of these, when coupled with established, or new compact modeling techniques like mixed Equation-Defined Device and Verilog-A models (VAEDD), make the current software a highly flexible and innovative platform for compact modeling and circuit simulation.

- Future improvements to the Qucs software indicate that by merging device parameter measurements with circuit simulation for device parameter extraction, and the introduction of EM field simulation with openEMS will significantly extend the scope of traditional circuit simulation.

Jahn S., and Brinson M., Interactive compact device modelling using Qucs equation defined devices, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, September/October 2008, 21(5), pp 335-349, DOI:10.1002/jnm.676.

References

Brinson M., and Jahn, Qucs: A GPL software package for circuit simulation, compact device modeling and circuit macromodeling from DC to RF and beyond, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, July/August 2009, 22(4), pp 207-319, DOI:10.1002/jnm.702.

Mike Brinson and Michael Margraf, Verilog-A compact semiconductor device modelling and circuit macromodelling with the QucsStudio-ADMS "Turn-Key" modelling system, International journal of Microelectronics and Computer Science, Vol. 3, No. 1, pp. 32-40, Jan. 2012. ISSN 2080-8755

Wladek Grabinski, Mike Brinson, Paolo Nenzi, Francesco Lannutti, Nikolaos Makris, Angelos Antonopoulos and Matthias Bucher, Open-source circuit simulation tools for RF compact semiconductor device modelling, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, Volume 27, Issue 5-6, September- December 2014, Pages: 761{779, DOI:10.1002/jnm.1973.

Mike Brinson and Vadim Kuznetsov, A new approach to compact semiconductor device modelling with Qucs Verilog-A analogue module synthesis, International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, Volume 29, Issue 6 November-December 2016, Pages 1070-1088, DOI: 10.1002/jnm.2166.

Mike Brinson and Vadim Kuznetsov, Extended behavioural device modelling and circuit simulation with Qucs-S, International Journal of Electronics, Volume 105, Issue 3, pp. 412-425, <u>http://dx.doi.org/10.1080/00207217.2017.1357764</u>.

Brinson, Mike (2019) FOSS Compact Model Prototyping with Verilog-A Equation-Defined Devices (VAEDD). In: 26th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), pp. 92-97, 27-29 June 2019, Rzeszow, Poland. DOI: 10.23919/MIXDES.2019.8787063, ISBN: 978-1-7281-3408-6.

Grabinski Wladek, Pavanello Marcelo, De Souza Michelly, Tomaszewski Daniel, Brinson Mike, Malesinska Jola, Głuszko Grzegorz, Bucher Matthias, Makris Nikolaos, Nikolaou Aristeidis, Abo-Elhadid Ahmed, Mierzwinski Marek, Lemaitre Laurent, Lallement Christophe, Sallese Jean-Michel, Yoshitomi Sadayuki, Malisse Paul, Oguey Henri, Cserveny, Stefan, Enz Christian, Krummenacher Franço and Vittoz Eric, 2019, FOSS EKV2.6 Verilog-A Compact MOSFET Model. Proceedings of ESSDERC 2019 - 49th European Solid-State Device Research Conference (ESSDERC). pp. 190-193. ISSN ISBN: 978-1-7281-1539-9.

Mike Brinson, The Qucs/QucsStudio and Qucs-S Graphical User Interface: An Evolving "White-Board" for Compact Device Modeling and Circuit Simulation in the Current Era: Invited Paper, In: 27th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), pp. 23-32, 25-27 June 2020, Wroclaw, Poland, ISBN: 978-83-63578-10-9.

Mike Brinson, Qucs-S/QucsStudio/Octave Schematic Synthesis Tools for Device and Circuit Parameter Extraction from Measured Characteristics. In: 26th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), pp. 50-55, 27-29 June 2019, Rzeszow, Poland. ISBN: 978-83-63578-18-3.

- □ **Qucs** Download version (Linux, Windows or Mac) as required from home page <u>http://qucs.sourceforge.net/</u>.

- □ **QucsStudio** Download Windows version QucsStudio-3.3.2.zip from <u>http://www.dd6um.darc.de/QucsStudio/download.html</u>.

- □ Qucs-S (Qucs with SPICE) Download version (Linux or Windows) as required from home page <a href="https://ra3xdh.github.io/">https://ra3xdh.github.io/</a>.

- □ **Xyce** Download version (Linux, Windows) as required from home page <u>https://xyce.sandia.gov/</u>.