# Adaptive EPFL-EKV Long and Short Channel MOS Device Models for Qucs, SPICE and Modelica Circuit Simulation

M.E. Brinson

Centre for Communications Technology London Metropolitan University London, UK Email: mbrin72043@yahoo.co.uk H. Nabijou Centre for Communications Technology London Metropolitan University London, UK Email: h.nabijou@londonmet.ac.uk

Abstract—Equation-defined non-linear functional elements are important building blocks in the development of compact semiconductor device models. Current trends in compact device modeling suggest widespread acceptance among the modeling community of Verilog-A, for semiconductor device specification, model exchange and circuit simulation. This paper outlines techniques for the development of adaptive EPFL-EKV long and short channel MOS models which stress user selectable model features and diagnostic capabilities. Adaptive EPFL-EKV nMOS models based on Verilog-A and Modelica are introduced and their performance compared with simulation data obtained using the "Quite universal circuit simulator" (Qucs), SPICE and the Modelica simulation environment.

*Index Terms*—Adaptive MOS models, Qucs, SPICE, Modelica, equation-defined device modeling, Verilog-A, EPFL-EKV MOS-FET model, parameter and equation monitoring.

#### I. INTRODUCTION

Compact semiconductor model development has in recent years advanced significantly through the use of equationdefined non-linear functional elements [1] and the adoption of Verilog-A as the hardware description language of preference for model construction and model interchange between different circuit simulators [2]. The standardization of Verilog-A [3] has also accelerated its acceptance as the modeling tool of choice among the compact device modeling community. In many respects Verilog-A is a hardware description language which has arrived on the modeling scene at the right time, bringing to the art of compact modeling an array of positive features which greatly aid in the construction of complex models. Such models appear to be characterized by an ever increasing number of parameters, particularly when compared to the number associated with the SPICE legacy devices [4]. These parameters, plus built-in model equations, allow accurate modeling of I-V, dynamic and noise characteristics for devices with sub-micron feature sizes. However, with current semiconductor device sub-micron feature sizes, model functionality is often achieved at the expense of model complexity [15]. Previous and current generations of circuit simulator normally allow users to select semiconductor device model types through the use of a LEVEL parameter. Similarly, in

some instances, model complexity can be controlled by setting one or more second order physical parameters to zero [5]. Unfortunately when the model code is not published, both these approaches do not give a clear indication as to the calculation overhead incurred by a given model, or a restricted subset model, making it difficult to minimize circuit simulation run times for a specific model hierarchical level. This paper outlines techniques for the development of adaptive long and short channel nMOS models which stress user selectable model features and promote diagnostic features through the addition of signal probes to model interfaces. Adaptive EPFL-EKV nMOS models based on Verilog-A and Modelica are introduced and their performance compared using simulation data obtained with Qucs [6] and the Modelica simulation environment [7], [8].

## II. THE BASIC LONG CHANNEL EPFL-EKV MOS MODEL

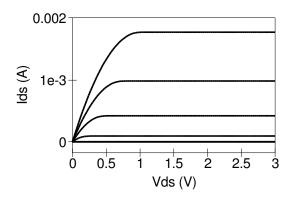

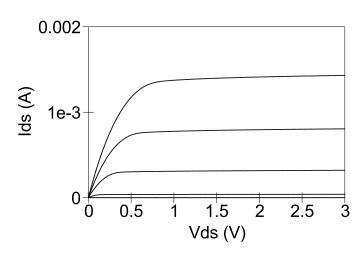

Ques equation-defined device (EDD) models and Verilog-A hardware description language models for long channel EPFL-EKV 2.6 nMOS transistors [9] can be found in recently published literature [10]. A set of typical long channel nMOS I-V characteristics obtained by Ques circuit simulation are presented in Fig. 1. As expected, both the Qucs EDD and the Verilog-A model simulation output data give identical results. However, one important difference between the performance of the two models is observed from the I-V simulation tests, namely the model simulation speed. The EDD model, being an interpretive model, tends to be slower than the Verilog-A model after its code has been translated to the C/C++ language, compiled and linked to the other sections of a circuit simulators C/C++ code. Ques is not the only simulator which allows compact semiconductor device models to be constructed with equation-defined components. Shown in Fig. 2 is the SPICE code for an EPFL-EKV long channel nMOS transistor based on the SPICE extensions implemented in LTspice IV (R) [11]. Unfortunately, at this time, there appears to be little standardization of the format for SPICE 3 extensions among the freely available General Public License (GPL) [12],[13] and commercial versions of SPICE, implying

Fig. 1. I-V output characteristic for a long channel EPFL-EKV 2.6 nMOS model with: L=0.5e-6m, W=10e-6m, VTO=0.6V, GAMMA=0.7 $\sqrt{V}$ , PHI=0.97V, KP=150e-6 $A/V^2$ , THETA = 50e-3 $V^{-1}$  and TEMP = 26.86 Celsius.

that the code shown in Fig. 2 would probably need some modification when run on a different SPICE simulator. It is also possible to develop a version of the EPFL-EKV 2.6 long channel nMOS transistor model using the Modelica simulation language. Fig. 3 presents the Modelica code for such a model. Like Verilog-A most implementations of the Modelica modeling environment are compiled, rather than interpretive, which results in fast circuit simulation speeds. Note how similar in many respects the Modelica language is to Verilog-A hardware description language.

# III. ADDING INTRINSIC CHARGE STORAGE EFFECTS TO THE LONG CHANNEL EPFL-EKV 2.6 MOS MODEL

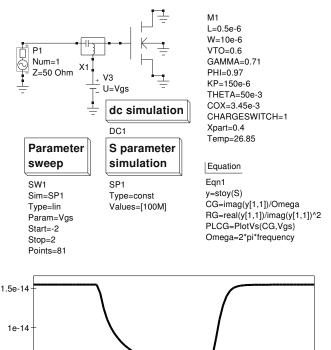

To be able to simulate the dynamic performance of MOS transistors a model for the device intrinsic stored charge or capacitance must be added to a DC MOS model. In the case of the EPFL-EKV 2.6 MOS model the stored charge is represented by equations (69) to (78) given in publication [9]. Fig. 4 presents the Verilog-A code for a long channel nMOS transistor with additional charge equation code. Device control parameter CHARGESWITCH is set to one if the charge calculation code is to be included in a simulation, otherwise it is set to zero and the charge code is ignored. The use of this type of switch allows a model to be adapted to fit the needs of a given simulation, for example at DC or very low frequencies the stored charge calculations can be removed from the model without loss of accuracy. The approach adopted in this paper ensures that switched out sections of Verilog-A code are not evaluated during simulation and hence improves the overall simulation speed of a model. It is also worth noting that the proposed code selection technique is ideal in the sense that it only adds a simulation speed penalty equivalent to the run time associated with a C/C++ "if-then-else" statement and a simple variable assignment statement. The test circuit and simulation results shown in Fig.5 indicate firstly how capacitance values can be extracted from a Ques model, either the equation-defined device or Verilog-A forms, using S parameter simulation techniques, and secondly how Qucs visualization procedures can be used to plot device intrinsic capacitance

Fig. 2. LTspice IV equation-defined non-linear subcircuit and I-V test circuit netlist for a long channel EPFL-EKV 2.6 nMOS model with identical parameters to those listed in Fig. 1.

| model EKV26nMOSLC<br>Modelica.Electrical.Analog.Interfaces.Pin D;<br>Modelica.Electrical.Analog.Interfaces.Pin G;<br>Modelica.Electrical.Analog.Interfaces.Pin S;<br>Modelica.Electrical.Analog.Interfaces.Pin B;<br>// Initialisation code<br>parameter Real L=5e-07; parameter Real W=1e-05;<br>parameter Real VTO=0.6; parameter Real PHI=0.97;<br>parameter Real VTO=0.6; parameter Real FHI=0.97;<br>parameter Real GAMMA=0.71; parameter Real TEMP=26.85;<br>constant Real PQ=1.602176462e-19; constant Real PK=1.3806503e-23;<br>parameter Real P1=-VTO+PHI+GAMMA*sqrt(PHI);<br>parameter Real P1=CATSMA/2; parameter Real VTT2=(PK*T2)/PQ;<br>parameter Real P5=PHI+4*VTT2; parameter Real VE1=(K*T2)/PQ;<br>parameter Real P5=PHI+4*VTT2; parameter Real P6=(KP*W)/L; |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>parameter Real P7=1/(2*VTT2); parameter Real P8=2*VTT2*VTT2;<br/>Real vgprime,vp, n, beta, iff1, iff, ir1, ir, ld;<br/>// Model equations and current contributions<br/>equation<br/>vgprime = G.v + P1;<br/>vp=if gprime&gt;0.0 then vgprime-PHI-GAMMA*(sqrt(vgprime+P3)-P2) else -PHI;<br/>n = 1 + P2 / sqrt(vp + P5);<br/>iff1 = log(1 + exp((vp - S.v) * P7)); iff = iff1 * iff1;<br/>ir1 = log(1 + exp((vp - D.v) * P7)); if = iff1 * iff1;<br/>ir1 = log(1 + exp((vp - D.v) * P7)); if = ir1 * ir1;<br/>beta= P6/(1+THETA*vp); Id = P8 * n * beta * (iff - ir);<br/>G.i = 0; D.i = Id; S.i = -Id; B.i = 0;<br/>end EKV26nMOSLC;</pre>                                                                                                                               |

Fig. 3. Modelica equation-defined non-linear model for a long channel EPFL-EKV 2.6 nMOS model with identical parameters to those listed in Fig. 1.

Cg = Cgs + Cgd + Cgb as a function of voltage Vgs. The same basic procedure can be adopted when developing a Mod-

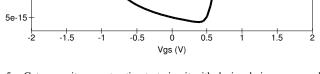

elica version of the EPFL-EKV 2.6 model. Presented in Fig.6 is the Modelica code equivalent to the Verilog-A version of the compact semiconductor device shown in Fig.4. In contrast to the Verilog-A model the Modelica model includes code for the device capacitance rather than device charge: equations 79 to 85 cited in publication [9]. Although the code for the two different hardware description languages looks similar a number of points are worth commenting on. Firstly, in the Verilog-A code the = and < + operators represent different forms of assignment statement. However, in the Modelica code the = operator is equivalent to the "equals" found in the notation for a mathematical equation. Secondly, again in the case of Modelica, the number of equations and the number of variables must balance for the code to simulate without error. This implies that there must only be one equation for each variable in a model. In the Modelica code given in Fig. 6 Verilog-A control variable CHARGESWITCH is replaced by CAPSWITCH and the Verilog-A time differential operator ddt by the equivalent Modelica operator der. Presented in Fig.7 is an example plot of a set of nMOS transistor intrinsic capacitances Cgs, Cgd, Cdb and Csb versus Vds obtained by Modelica simulation.

| `include "disciplines.vams"                                                            |  |  |

|----------------------------------------------------------------------------------------|--|--|

| `include "constants.vams"                                                              |  |  |

| module EKV26nMOSSC1(drain,gate,source,bulk);                                           |  |  |

| inout drain,gate,source,bulk; electrical drain,gate,source,bulk;                       |  |  |

| parameter real L=0.5e-6 from [1e-20:inf];                                              |  |  |

| parameter real W=10e-6 from [1e-20:inf];                                               |  |  |

| parameter real VTO=0.6 from [1e-20:2.0];                                               |  |  |

| parameter real GAMMA=0.71 from [0:2.0];                                                |  |  |

| parameter real PHI=0.97 from [0.3:2.0];                                                |  |  |

| parameter real KP=150e-6 from [1e-20:inf];                                             |  |  |

| parameter real THETA=50e-3 from [0:inf];                                               |  |  |

| parameter real DW=-0.02e-6 from [-5e-6:0];                                             |  |  |

| parameter real DL=-0.05e-6 from [-5e-6:0]:                                             |  |  |

| parameter real COX=3.45e-3 from [1e-20:inf];                                           |  |  |

| parameter real TEMP=26.85 from [-100: 100];                                            |  |  |

| parameter integer CHARGESWITCH=0 from [0:1];                                           |  |  |

| parameter real Xpart=0.4 from [0:1];                                                   |  |  |

| real P1,P2,P3,P5,P6,P7,P8,P9, P10; real vgprime,vp,n,beta,iff1,ir1,iff,ir, weff, leff; |  |  |

| real ng,P21,xf,xr,qi,qb,qg,coxide,Qi,Qb,Qg,Spart;                                      |  |  |

| branch (gate, bulk) Bgb; branch (source, bulk) Bsb; branch (drain, bulk) Bdb;          |  |  |

| branch (drain, source) Bds; branch (gate, drain) Bgd; branch (gate, source) Bgs;       |  |  |

| analog begin                                                                           |  |  |

| @(initial model) begin                                                                 |  |  |

| P1=-VTO+PHI+GAMMA*sqrt(PHI); P2=GAMMA/2; P3=P2*P2; P10=4*\$vt;                         |  |  |

| P5=PHI+4*\$vt+1e-12; P6=KP*W/L; P7=1/(2*\$vt); P8=2*\$vt*\$vt;                         |  |  |

| weff=W+DW; leff=L+DL; P21=PHI+1e-6;                                                    |  |  |

| Spart=1-Xpart; coxide=COX*weff*leff;                                                   |  |  |

| end                                                                                    |  |  |

| vgprime=V(Bgb)+P1;                                                                     |  |  |

| if (vgprime>0.0) vp=vgprime-PHI-GAMMA*(sqrt(vgprime+P3)-P2); else vp=-PHI;             |  |  |

| n=1+P2/sqrt(vp+P5);                                                                    |  |  |

| iff1=ln(1+limexp((vp-V(Bsb))*P7)); iff=iff1*iff1;                                      |  |  |

| ir1=ln(1+limexp((vp-V(Bdb))*P7)); ir=ir1*ir1;                                          |  |  |

| // Charge equations                                                                    |  |  |

| if ((CHARGESWITCH==1) begin                                                            |  |  |

| nq=1+GAMMA/(2*sqrt(vp+P21)); xf=sqrt(0.25+iff); xr=sqrt(0.25+ir);                      |  |  |

| qi=-nq*(1.333333*(xf*xf+xf*xr+xr*xr)/(xf+xr+1e-20)-1);                                 |  |  |

| if (vgprime > 0) qb=(-GAMMA*sqrt(vp+P21))/\$vt-((nq-1)/nq)*qi;                         |  |  |

| else qb=-vgprime/\$vt;                                                                 |  |  |

| qg=-qi-qb;                                                                             |  |  |

| end                                                                                    |  |  |

| if (CHARGESWITCH==1) begin                                                             |  |  |

| Qi=coxide*\$vt*qi; Qb=coxide*\$vt*qb; Qg=coxide*\$vt*qg;                               |  |  |

| I(Bgd) <+ Spart*ddt(Qg); I(Bgs) <+ Xpart*ddt(Qg);                                      |  |  |

| l(Bdb) <+ Spart*ddt(Qb); l(Bsb) <+ Xpart*ddt(Qb);                                      |  |  |

| end;                                                                                   |  |  |

| vpdash=0.5*(vp+sqrt(vp*vp+P8)); beta=P6/(1+THETA*vpdash);                              |  |  |

| I(Bds) <+ P8*n*beta*(iff-ir);                                                          |  |  |

| end                                                                                    |  |  |

| endmodule                                                                              |  |  |

Fig. 4. Verilog-A non-linear long channel EPFL-EKV 2.6 nMOS DC model plus device intrinsic capacitance modeled as intrinsic, gate and bulk charge: default device parameters are listed in the initial section of the model

Cg (F)

Fig. 5. Gate capacitance extraction test circuit with device drain, source and bulk terminals connected to ground and waveform Cg = Cgs+Cgd+Cgb (F) plotted against Vgs (V) at a test frequency of 100MHz and -2V  $\leq Vgs \leq 2V$ .

# IV. EXTENDING THE VERILOG-A AND MODELICA VERSIONS OF THE EPFL-EKV 2.6 MOS MODEL TO INCLUDE SHORT CHANNEL EFFECTS

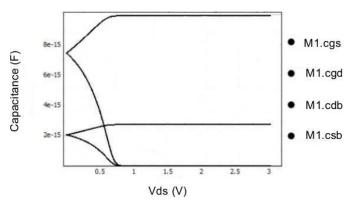

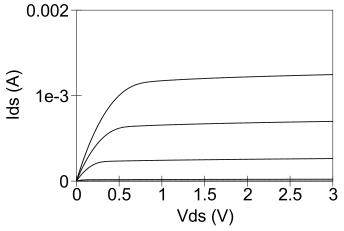

Verilog-A and Modelica short channel versions of the long channel EPFL-EKV 2.6 MOS model previously described are introduced in this section. The proposed short channel model includes the four switches listed in Table I. The purpose of these switches is to select the short channel effects that are to be included in the model during simulation: when the switches are set to one the corresponding short channel effect is active. The reverse is true when the switches are set to zero. Using the Verilog-A and Modelica code presented in Fig.4 and Fig.6 as a template allows short channel MOS models to be easily constructed from the equations listed in the reference cited in Table I. The set of nMOS transistor output curves drawn in Fig. 8 and Fig. 9 give an indication of the effects that adding short channel features to the EPFL-EKV 2.6 MOS model have on nMOS I-V output characteristics. The data shown in Fig. 8 and Fig. 9 applies to both the Verilog-A and Modelica short channel EPFL-EKV 2.6 models. Figure 8 shows the effect channel-length modulation has on the nMOS I-V output characteristics where the relative channel length reduction depends on the pinch-off point at the MOSFET channel drain end of the device. In the EPFL-EKV 2.6 model the channel-length modulation effect is modeled by

Fig. 6. Modelica non-linear long channel EPFL-EKV 2.6 nMOS DC model plus device intrinsic capacitances Cgs, Cgd, Cdb and Csb: default device parameters are listed in the initialization section of the model

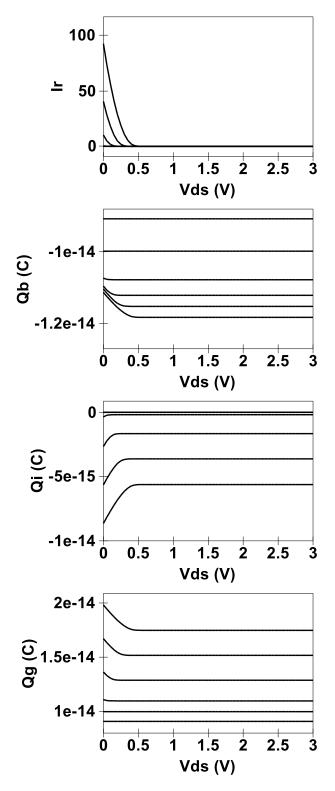

Fig. 7. Individual values for Modelica simulated nMOS intrinsic capacitances Cgs, Cgd, Cdb and Csb plotted as a function of Vds over the range  $0 \ll$  Vds  $\ll 3V$ : default device parameters as listed in the initialization section of the model given in Fig.6

the depletion length coefficient parameter LAMBDA. Fig. 9 presents the I-V output characteristics for a device where all the short channel model effects have been include by setting all the model control switches to one. Although the differences between the curves shown in Fig. 8 and Fig. 9

appear small they can have a significant effect on device performance at very high frequencies. With reduced device feature sizes, compared to the parameters given in Fig. 1, inclusion of short channel effect becomes essential for accurate circuit simulation.

TABLE I

CONTROL SWITCHES FOR SELECTING SHORT CHANNEL EFFECTS

| Switch     | Short channel effect                                                       | Equations<br>(in publication[9]) |

|------------|----------------------------------------------------------------------------|----------------------------------|

| CLMSWITCH  | Channel length modulation                                                  | 58 to 62                         |

| TFMRSWITCH | Transconductance factor and<br>mobility reduction due to<br>vertical field | 46, 48 to 55                     |

| CHSHSWITCH | Charge sharing for short<br>narrow channels                                | 34 to 38                         |

| RSCESWITCH | Reverse short channel effect                                               | 30 to32                          |

Fig. 8. Typical nMOS transistor output characteristics showing the effects caused by setting short channel control switches: CLMSWITCH=1, TFRMR-SWITCH=0, CHSHSWITCH=0, RSCESWITCH=0 and CHARGESWITCH or CAPSWITCH=0

Fig. 9. Typical nMOS transistor output characteristics showing the effects caused by setting short channel control switches: CLMSWITCH=1, TFRMR-SWITCH=1, CHSHSWITCH=1, RSCESWITCH=1 and CHARGESWITCH or CAPSWITCH=0

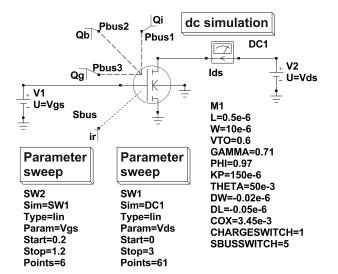

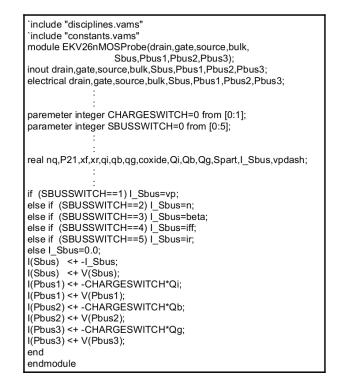

# V. ADDING PROBES TO VERILOG-A COMPACT SEMICONDUCTORS FOR MONITORING DEVICE PERFORMANCE DURING SIMULATION

One of the most striking differences between Verilog-A and current implementations of the Modelica hardware description language is the ability of the latter to automatically record, during simulation, values for all the variables that contribute to a set of model equations. This allows a complete post simulation analysis of the performance of a model to be undertaken easily as part of a model validation sequence. One approach with Verilog-A to obtain values for model internal signals, equations and variables is to add extra signal nets to a model interface as part of the Verilog-A module statement. These nets act as data highways for internal model probes. Two obvious types of signal probe structure can be built into Verilog-A compact device models: firstly parallel signal probes with one probe per signal or internal variable, and secondly serial signal probes which can be switched to monitor specific signals by setting the value of a control variable prior to simulation. In practice, a combination of both parallel and serial probes are often employed to give coverage of a range of internal device signals and variable values, with priority signals connected to parallel probes. Figure 10 illustrates a typical combined parallel and series model probe configuration, here different line styles are employed to indicate the parallel and serial probes. Fig. 11 shows the Verilog-A code for the parallel and serial probe signal highways and the internal model quantities being monitored. Notice that setting variable SBUSSWITCH to zero disables the serial monitoring bus and setting CHARGESWITCH to zero also disables the parallel monitoring bus. Fig. 12 shows a typical group of internal model signals obtained from transistor output characteristic simulation tests.

Fig. 10. EPFL-EKV 2.6 nMOS transistor I-V output characteristic test circuit with parallel and serial data monitoring bus structures

Fig. 11. Serial and Parallel signal monitoring Verilog-A code for a long channel EPFL-EKV 2.6 nMOS transistor model: Only those lines of code which need to be modified or added to the Verilog-A code given in Fig. 4 are listed

#### VI. CONCLUSION

Adaptive versions of complex compact semiconductor models promote simplified device modeling via user selective equation-defined model structures. This type of compact model provides users with the opportunity to select device features which are "custom built" to meet the requirements of specific types of circuit simulation. In reality, when selecting model features, there is a trade off between model complexity and simulation speed, which in turn encourages users to select a model with minimum complexity that offers improved simulation speed. This paper outlines the adaptation of the well known EPFL-EKV 2.6 MOS model as a structured semiconductor device model, while simultaneously presenting Verilog-A and Modelica simulation data which illustrates some of properties, and advantages, of modular compact device models.

#### ACKNOWLEDGEMENT

The material reported in this paper forms part of the work done in response to the MOS Modeling and Parameter Extraction Working Group (MOS-AK) Verilog-A compact modeling standardization initiative [14]. The authors would like to thank ITI, GmbH Germany for providing copies of their SimulationX [8] software for part of the Modelica study reported in this paper.

Fig. 12. A typical set of serial and parallel monitoring bus signals plotted as a function of Vds: SBUSSWITCH=5, CHARGESWITCH=1 and other parameters the same as those given in Fig. 10

#### References

M.E. Brinson and S. Jahn, "Ques: A GPL software package for circuit simulation, compact device modeling and circuit macromodelling from DC to RF and beyond", International Journal of Numerical Modelling: Networks, Devices and Fields, vol. 22, pp. 297-319, 2009.

- [2] L. Lemaitre, W. Grabinski and C. McAndrew, "Compact device modeling using Verilog-A and ADMS", Electron Technology Internet Journal, Vol 35, pp1-5, 2003.

- [3] Accellera, "Verilog-AMS Language Reference Manual, Version 2.3', 2008, http://www.accellera.org/activities/verilog-ams [accessed March 2011].

- [4] W. Grabinski, M. Brinson, S. Mijalkovic, D. Pattullo and M.Pronath, "Panel Discussion: Better analog modeling and integration with iPDKs", GSA European Analog/Mixed-Signal and Modeling Technical Workshop, GSA and IET International Semiconductor Forum, London, UK, May 18-19, 2010.

- [5] B. Johnson, T. Quarles, A.R. Newton, D.O. Pederson and A. Sangiovanni-Vincentelli, "SPICE3 Version 3f User's Manual, Department of Electrical Engineering and Computer Science, University of California, Berkeley, CA, 1992.

- [6] M. Margraf, S. Jahn, J. Flucke, R. Jacob, V. Habchi, T. Ishikawa, A. Gopala Krishna, M. Brinson, H. Parruitte, B. Roucaries, and G. Kraut, "Ques (Quite universal circuit simulator)", 2003, http://ques.sourceforge.net/index.html, [accessed March 2011].

- [7] Open Source Modelica Consortium (OSCM), "OpenModelica", http://www.openmodelica.org/, [accessed March 2011].

- [8] ITI GmbH, Germany, "SimulationX 3.3", http://www.simulationx.com, [accessed March 2011].

- [9] M. Bucher, C. Lallement, C. Enz, F. Théodoloz and F. Krummenacher, "The EPFL-EKV model equations for simulation, v2.6" Electronics Laboratories, Swiss Federal Institute of Technology, Lausanne (EPFL), Switzerland, 1997.

- [10] M.E. Brinson and S. Jahn, "Compact device modeling for established and emerging technologies with the Ques GPL circuit simulator", MIXDES 2009, 16 International Conference, Mixed Design of Integrated Circuits, Lódź, Poland, June 25-27, 2009.

- [11] Linear Technology, "LTspice IV",

- http://www.linear.com/designtools/software/, [accessed March 2011].

- [12] Spice OPUS Homepage, http://www.fe.uni-lj.si/spice, [accessed March 2011].

- [13] P. Nezi, et al., "ngspice", http://www.ngspice.sourceforge.net/index.html, [accessed March 2011].

- [14] S. Jahn, M. Brinson, H. Parruitte, B. Ardouin, P. Nenzi and L. Lemaitre, "GNU simulators supporting Verilog-A compact model standardization", MOS-AK meeting, Premstaetten 2007, http://www.mosak.org/premstaetten/papers/MOSAK\_QUCS\_ngspice\_ADMS.pdf, [accessed March 2011].

- [15] G. Gildenblat, "Compact Modeling, Principles, Techniques and Applications", Springer, Dordrecht, Heidelberg, London, New York. 2010.