### Modeling of GaN HEMTs With Open Source Qucs-S Circuit Simulation and Compact Device Modeling Technology

Mike Brinson<sup>1</sup>, mbrin72043@yahoo.co.uk. Vadim Kuznetsov<sup>2</sup>, ra3xdh@gmail.com

<sup>1</sup>Centre for Communications Technology, London Metropolitan University, UK

<sup>2</sup>Bauman Moscow Technical University, Russia

Presented at IEEE EDS mini-Colloquium on GaN HEMT Technology , Lodz, 22 June 2016

# Modeling of GaN HEMTs With Open Source Qucs-S Circuit Simulation and Compact Device Modelling Technology: Presentation Content

- Qucs-0.0.19-S-RC6 Simulation and Compact Device Modelling Tools

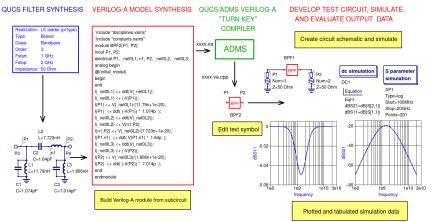

- Introduction to the Qucs GPL Verilog-A Module Synthesizer

- Qucs modelling of the "Efficient Power Corporation (EPC)" GaN EPC2001 Power Transistor

- Qucs Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT Compact Device Model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data

- Qucs-0.0.19-S-RC6 XSPICE Code Modeling package

- Qucs-0.0.19-S-RC6/Ngspice/Xyce Circuit Analysis and Compact Device Parameter Extraction from Manufacturers Data or Measurements Controlled by Octave Script Files

- Summary

### Qucs-0.0.19-S-RC6 Simulation and Compact Device Modelling Tools

$\mathsf{Qucs}\text{-}0.0.19\text{-}\mathsf{S}\text{-}\mathsf{RC6}$  includes the  $\mathsf{Qucs}$  GPL Verilog-A synthesis tool for compact device modelling.

- The Qucs-0.0.19-S-RC6 Verilog-A synthesizer is a fully working version of this new open source ECAD tool.

- It is for test purposes: bugs are likely but it is now more stable than the initial release.

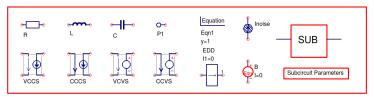

- Verilog-A device models and circuit macromodels can be synthesized from the following Qucs/SPICE built in components:

### Introduction to the Qucs GPL Verilog-A Module Synthesizer: Part II

Structure:

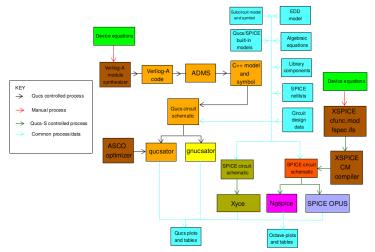

#### Data flow through the Qucs GPL compact device modelling tool set.

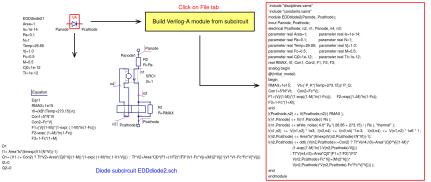

Synthesis of a SPICE like compact semiconductor diode model: EDD static  $I_d$ and dynamic capacitance model ---- synthesized Verilog-A module code

D1

### Introduction to the Qucs GPL Verilog-A Module Synthesizer: Part V

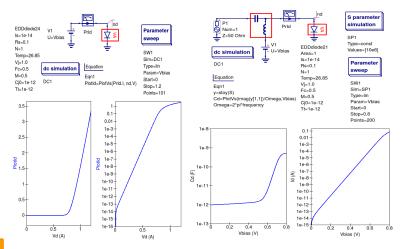

Synthesis of a SPICE like semiconductor diode model: simulated static and dynamic characteristics.

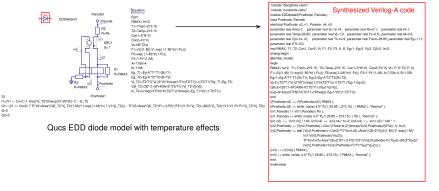

### Verilog-A synthesis of a SPICE like semiconductor diode model: temperature effects

#### Introduction to the Ques GPL Verilog-A Module Synthesizer: Part VII

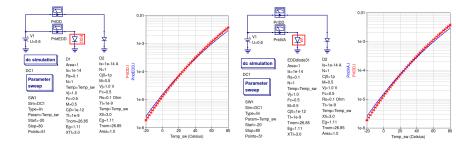

Verilog-A synthesis of a SPICE like semiconductor diode model: simulated  $I_d - V_d$  temperature effects.

#### Simulation data for Qucs EDD model and built-in diode model

Simulation data for Verilog-A model and built-in diode model 0

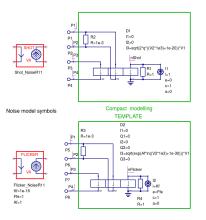

Verilog-A synthesis of semiconductor device shot and flicker noise: EDD models and Verilog-A module code.

| $\begin{split} & \ (nShot) < + (V(nShot))(1); \\ & \ (nShot) < + white noise(1, "shot"); \\ & \ (P2,P1) < (V(P2,P1))((1e3); \\ & \ (P3,P4) < + sqrt(2^*P_{0}^*)((V(P1,P2)^*1e3)+1e\cdot20))^*V(nShot); \\ & end module \end{split}$ | Include "disciplines vams"<br>Include "constants vams"<br>module 8hc, Nosel (PJ, P2, P3, P4);<br>Inout P1, P2, P3, P4;<br>electrical n8hc+(P2, P1, P3, P4;<br>analog begin<br>@(initial_model)<br>begin<br>end |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                                                                                                                                     | $\label{eq:product} \begin{split} & I(P2,P1) < + V(P2,P1)/(\ 1e{\cdot}3\ ); \\ & I(P3,P4) < + sqrt(2^{**}P_{Q}^{*}((V(P1,P2)^{*}1e{\cdot}3){+}1e{\cdot}20))^{*}V(n3) \\ & end \end{split}$                     | Shot); |

#### Synthesized Verilog-A module code

Verilog-A synthesis of semiconductor device shot and flicker noise: small signal AC domain simulation data.

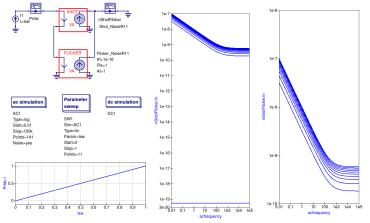

Verilog-A synthesis of multi-EDD models: EKV2p6 nMOS  $I_{ds} = f(V_d, V_g, V_s, V_b)$  model for a transistor operating in long channel mode.

Qucs EDD EKV2p6 lds=f(Vd, Vg, Vs, Vb) model

Synthesized EKV2p6 lds=f(Vd, Vg, Vs, Vb) Verilog-A code

#### Introduction to the Qucs GPL Verilog-A Module Synthesizer: Part XI

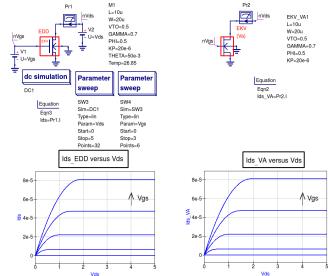

Verilog-A synthesis of multi-EDD models: EKV2p6 nMOS  $I_{ds} = f(V_d, V_g, V_s, V_b)$  swept DC simulation data.

1 - 2

14 / 40

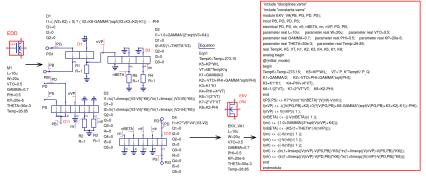

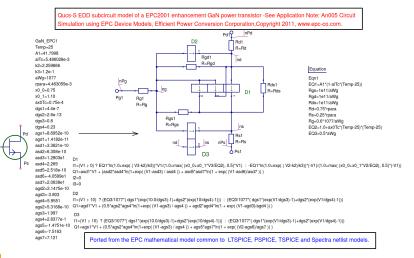

#### Ques modelling of the "Efficient Power Corporation (EPC)" GaN EPC2001 Power Transistor: Part I EDD Subcircuit Compact Device Model

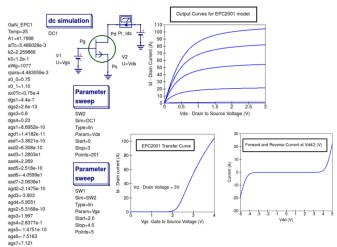

#### Ques Modeling of the "Efficient Power Corporation (EPC)" GaN EPC2001 Power Transistor: Part II DC Test Bench and Typical Simulation Curves

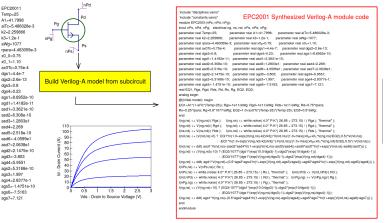

#### Ques Modeling of the "Efficient Power Corporation (EPC)" GaN EPC2001 Power Transistor: Part III Synthesis of Verilog-A code for a EPC2001 Ques EDD subcircuit

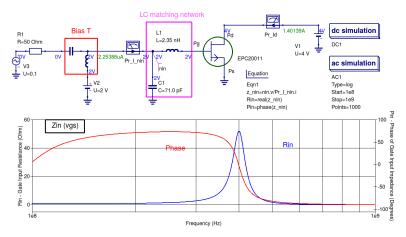

Ques Modeling of the "Efficient Power Corporation (EPC)" GaN EPC2001 Power Transistor: Part IV AC Gate Matching Network Test Bench and Typical Simulation Results

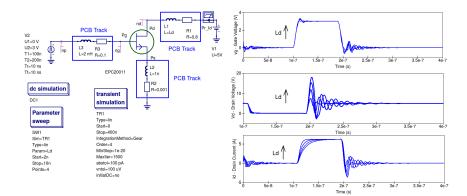

Ques Modelling of the "Efficient Power Corporation (EPC)" GaN EPC2001 Power Transistor: Part V Switching Response Test Bench and Typical Simulation Results

### Ques Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT Compact Device Model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data - Part I Introduction

- The Analogue Device Model Synthesizer (ADMS) version 2.3.5 is used by Qucs, Ngspice, Xyce and Gnucap GPL circuit simulators for Verilog-A compact semiconductor device modeling.

- ADMS is based on a subset of Verilog-A HDL selected for compact device modeling.

- Although the Verilog-A HDL is standardised there is no guarantee that individual simulator implementations allow the same dialect of Verilog-A for modeling purposes, for example Qucs Verilog-A models can include component noise while Ngspice does not implement thermal, shot or flicker noise.

- Normally emerging technology Verilog-A compact models have to be modified, often by hand, to compile without error: specific areas which can cause problems are

- Internal node collapsing,

- Voltage limiting,

- Setting initial conditions,

- Model equations that include complex combinations of analogue functions,

- Thermal effects due to power dissipation.

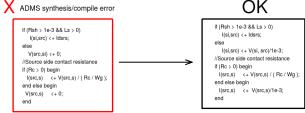

Qucs Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT Compact Device Model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data - Part II Model Parameter Statement Error Work-Arounds

ADMS parameter statements DO NOT ALLOW reference to previously defined model parameters.

ADMS synthesis/compile error

OK

| parameter real | vxord    | - 1.30e7  | from (0:inf):   | // Source injection velocity (cm/s)                                      |         |

|----------------|----------|-----------|-----------------|--------------------------------------------------------------------------|---------|

| parameter real |          | = -2.0:   |                 | id voltage of drain access transistor[V]                                 |         |

| parameter real |          | - 5.0e-7  | from (0:inf):   | // Drain access areal capacitance [F/cm2]                                |         |

| parameter real |          |           | from (0:inf);   | // DIBL for drain access transitor                                       |         |

| parameter real |          |           | from (0:inf);   | // DIBL for drain access transitor                                       |         |

|                |          |           |                 | // DIBL for drain access transitor<br>// DIBL for drain access transitor |         |

| parameter real |          |           | from (0:inf);   |                                                                          |         |

| parameter real |          |           | from [0:inf);   | // Subthreshold slope for drain access transitor [V/Dec                  |         |

| parameter real |          |           | from (0:Inf);   | // Self heating parameter (scalable)                                     |         |

| parameter real | betard   | = 1.3     | from (0:inf);   | // Linear to saturation transition parameter                             |         |

| parameter real | vthetard | - 0.05    | from (0:Inf);   | // Scattering: velocity reduction parameter with Vg                      |         |

| parameter real | ndrd     | = 0*0.80  | from (0:inf);   | // Punchthrough factor affects slope change in subth                     | reshold |

|                |          |           |                 |                                                                          |         |

| parameter real | vxors    | - vxord   | from (0:inf);   | // Source injection velocity [cm/s]                                      |         |

| parameter real | VtOrs    | = VtOrd;  | // TI           | hreshold voltage of drain access transistor[V]                           |         |

| parameter real | Ogrs     | - Cgrd    | from (0:Inf);   | // Drain access areal capacitance [F/cm2]                                |         |

| parameter real | delta1rs | = delta1r | d from (0:inf); | // DIBL for drain access transitor                                       |         |

| parameter real | delta2rs | - delta2r | d from (0:inf); | // DIBL for drain access transitor                                       |         |

| parameter real | Srs      | - Srd     | from (0:inf);   | // Subthreshold slope for drain access transitor [V/Dec                  |         |

| parameter real | vthetars | = 0.05    | from (0:inf);   | // Scattering: velocity reduction parameter with Vg                      | ·       |

| parameter real |          |           | from (0:Inf):   | // Punchthrough factor affects slope change in subthr                    | eshold  |

| parameter real | betars   | = betard  | from (0:inf);   | // Linear to saturation transition parameter                             |         |

| parameter real |          |           | moni formite    | a circa to caloratori tranonori parameter                                |         |

Ques Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT Compact Device Model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data - Part III Removing V(n) < +statements

- ADMS DOES NOT ALLOW voltage contributions of the form V(n) < +I(n) \* R, where R is a resistance in  $\Omega$ ,

- OR statements of the form V(n) < +0.0,

- Resistors, for example  $0.001\Omega$ , are used to short nodes (node collapsing), with I(n) < +V(N)/0.001.

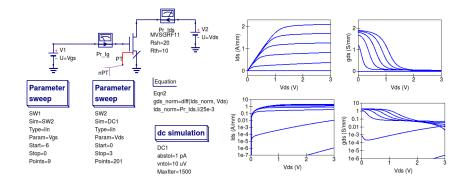

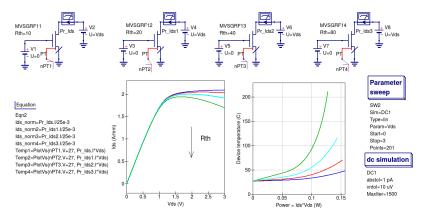

Ques Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT compact model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data - Part IV DC Characteristics

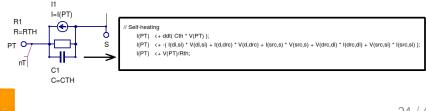

Ques Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT compact model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data - Part V Simulating Thermal self-Heating Effects Induced by Internal Power Dissipation

- The ADMS dialect of Verilog-A does not implement the pwr(dt) statement,

- Device self-heating is often modelled with a parallel RC network where the volt drop across the RC combination represents the change in device temperature due to internal power dissipation,

- $Tth = Rth \cdot Pd + Temp(Pd = 0)$ , where Tth is the device temperature at power dissipation Pd (W).

Ques Verilog-A Modeling of the "MIT Virtual Source GaN-RF HEMT compact model 1.0.0": Problems Simulating with ADMS; Workarounds and Typical Simulation Data - Part VI Variation of Thermal Resistance Rth and its Effect on DC Characteristics

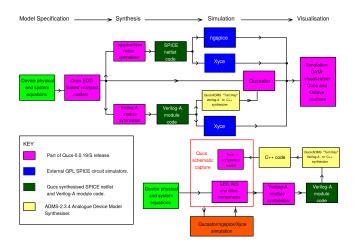

Qucs-0.0.19-S-RC6 Modeling Tool Additions and New Features Currently Under Development: Moving Forward to the Next Generation of Qucs-S Circuit Simulation and compact Device Modeling Capabilities

- Qucs-0.0.19-S-RC6 includes for the first time a "turn-key" XSPICE Code Modelling package for use with the Ngspice and SPICE OPUS circuit simulators,

- Qucs-0.0.19-S-RC6 is being extended to include a new Qucs/Octave integrated tool set for compact device model and circuit macromodel parameter extraction with data fitting and optimization using measured, or manufacturer's published device data, and simulated circuit data this new feature is experimental, but should become more stable during the summer 2016 development period.

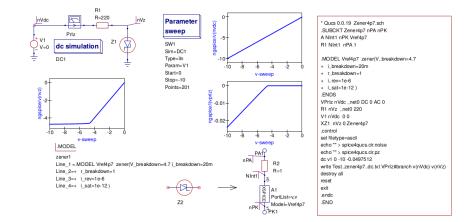

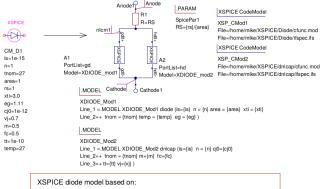

### Qucs-0.0.19-S-RC6 XSPICE Code Modeling package: Part I XSPICE Code Model Subcircuits

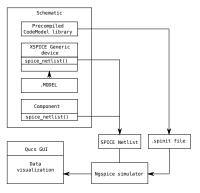

### Qucs-0.0.19-S-RC6 XSPICE Code Modeling Package: Part II XSPICE CodeModel Support Subsystem

- The "XSPICE generic device" component is the foundation for

- Precompiled XSPICE device (\*.cm) library support, and

- Dynamic XSPICE Code Models compilation system which allows Code Model sources to be attached to a schematic and compiled automatically at simulation time.

• Precompiled Code Model \*.cm library attachment data flow diagram

### Qucs-0.0.19-S-RC6 XSPICE Code Modeling package: Part III "XSPICE Generic Device" Component

• The "XSPICE generic device" component is a building block for the construction of user-defined A-devices. It is defined by a comma separated port list, with allowed XSPICE port designators, then attached to a SPICE .MODEL statement

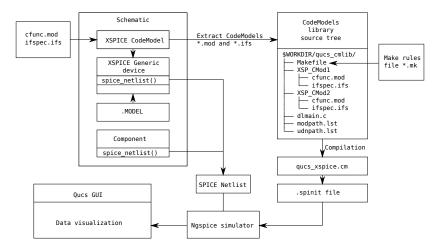

## Qucs-0.0.19-S-RC6 XSPICE Code Modeling Package: Part IV XSPICE "Turn-Key" Model Generation; Compiler System Dataflow Diagram

# Qucs-0.0.19-S-RC6 XSPICE Code Modeling Package: Part V XSPICE Diode Model - (a) The Qucs-S subcircuit Symbol and Model Circuit

- P. Antognetti and G. Massobrio (Editors), "Semiconductor device modeling with SPICE, 1988, McGraw-Hill Book Componey, New York, pp1-32.

- S. Jahn amd M.E. Brinson, "Interactive device modelling using Ques equation-defined devices., 2008, International Journal of Numerical Modelling: Electrical Networks, Devices and Fields, 21:335-249, DOI: 10.1002/jnm.676.

### Qucs-0.0.19-S-RC6 XSPICE Code Modeling Package: Part V XSPICE Diode Model - (b) The XSPICE Diode/func.mod Code

```

diode cm model. 4 March 2016 Mike Brinson

if(INIT) {

cm_analog_alloc(DERIVE, sizeof(double));

This file contains the mode code for an experimental semiconductor diode model.

derive = (double *)cm_analog_get_ptr(DERIVE, 0);

This is used as a test bench for constructing compact device models

*derive = 0.0;

using the Qucs-0.0.19-S automatic XSPICE CodeModel compiler system.

else (

This is free software; you can redistribute it and/or modify

derive = (double *)cm_analog_get_ptr(DERIVE, 0);

it under the terms of the GNU General Public License as published by

the Free Software Foundation: either version 2, or (at your option)

any later version

if ANALYSIS != AC) /

Vd = INPUT(diode)

#define DERIVE 0

if (Vd > P3*Vt temp) {

#include <math.h>

if (P1*Vd <= 80) {

void cm_diode(ARGS)

Id = is temp*(exp(P1*Vd)-1.0) + GMIN * Vd:

OUTPUT(diode) = Id;

double Vt.temp, Vd. P1, P3, P4, PTNOM, PTEMP;

*derive = P1*Is_temp*exp(P1*Vd)+GMIN;

double PIS, PAREA, PXTI, PEG, PN;

PARTIAL(diode, diode) = *derive:

double Tr. Is temp. Id:

double *derive-

else {

double exp80 = 5,5406334e34;

Id = is temp*exp80*(1+(P1*Vd-80))+GMIN*Vd:

double GMIN = 1e-12:

OUTPUT(diode) = Id:

*derive = P1*P4+ GMIN

PTNOM = PARAM(tnom)+273.15:

PARTIAL (diode, diode) = *derive:

PTEMP = TEMPERATURE+273.15:

Vt..temp = 8.65387195e-5*PTEMP:

PEG = PARAM(eg);

if ( Vd <= -5*PN*Vt temp)

PIS = PARAM(is):

Id = -ls_temp+GMIN*Vd;

PN - PARAM(n)

OUTPUT(diode) = Id;

PAREA = PARAM(area):

*derive = GMIN

PXTI = PARAM(xti)

PARTIAL(diode, diode) = *derive;

P1 = 1/(PN*Vt_temp);

Tr = PTEMP/PTNOM

Is..temp = PAREA*PIS*exp( (PXTI/PN)*log(Tr))*exp( (-PEG/Vt..temp)*(1.0-Tr));

P3 = -5*PN:

P4 = Is_temp*exp80;

```

Semiconductor diode non-linear I<sub>d</sub> / V<sub>d</sub> characteristics, including Verilog-A limexp function and temperature effects.

# Qucs-0.0.19-S-RC6 XSPICE Code Modeling package: Part VI XSPICE diode model - (c) The XSPICE Non-Linear Diode Capacitance dnlcap/func.mod Code

/\* dnicap.cm.model. 4 March 2016 Mike Brinson This file contains the model code for an experimental semiconductor diode capacitance: both Cdep and Cdiff are modelled. This is used as a test bench for constructing compact device models. with the Ours-0 0 19-S automatic XSPICE CodeModel compiler system This is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation: either version 2, or (at your option) any later version #teline CVC 0 stoclude creath by void cmunicap(ARGS) Complex\_t ac\_gain: static double PCJ0, PVJ, PM, PEC, PTT, PIS, PN double P1 Vd partial Vt temp: double PTEMP, W1, Wr, Wi, Rd; double "our static double cap, F2, F3, cdep, derive, Id, P3, P4; double Rp = 1.0e12; double exp80 = 5.5406334e34; double GMIN = 1e-12 PTEMP = TEMPERATURE+273 15: Vtemp = 8.65387195e-5\*PTEMP; P1 = 1/(Vt\_temp); if(INIT ==1) { cm.nalog alloc(CVC, sizeof(double)); cvc = (double \*) cm..analog.get.ptr(CVC, 0); "cvc = 0.0: can = 1e.16 derive = 1e-20 PCJ0 = PARAM(ci0): PVJ = PARAM(vi); PM = PARAM(m): PEC = PARAM(Ic): PTT = PARAM(tt); PIS - PARAM(s) PN = PARAM(n); F2 = exp( (1+PM)\*log(1-PFC) ); F3 = 1-PEC\*(1+PM): P3 = -5\*PN P4 = PIS\*exn80:

else ( cvc = (double ") cm\_analog\_get\_ptr/CVC.0); If (ANALYSIS != AC) [ Vd = "cvc; if (Vd > P3\*Vt.temp) { if (P1\*Vd <= 80) { Id = PIS\*(exp(P1\*Vd)-1.0) + GMIN \* Vd derive = P1\*PIS\*exp(P1\*Vd)+GMIN else { Id = P4\*(1+(P1\*Vd-80))+GMIN\*Vd; derive = P1\*P4+GMIN: else l Id = \_PIS+GMIN\*V/t derive - GMIN Semiconductor diode If (Vd < PFC\*PVJ) ( cden = PCJ0/exp(PM\*log(1.0 - (Vd/PVJ))); non-linear capacitance characteristics. else cdep = (PCJ0/F2)\*(F3+(PM\*Vd/PVJ)); including depletion cap = PTT\*Id/Vtemp + cdep and diffusion components if (ANALYSIS == DC) ( "rwn = INPLIT(dnican)"Bro OUTPUT(dnicap) = "cvc; PARTIAL(dnicap, dnicap) = Rp If (ANALYSIS == TRANSIENT) ( cm\_nalogntegrate(INPUT(dnlcap) / (cap + 1e-17), cvc, &partial); partial /= cap; OUTPUT(dolcan) = "cvm: PARTIAL(dnicap, dnicap) = partial; if (ANALYSIS == AC) ( W1 = 1+RAD\_FREQ\*RAD\_FREQ\*Rd\*Rd\*cap\*cap; Wr = RdW1 Wi = RAD\_REQ\*cap\*Rd\*Rd/W1; ac...qain.real = Wr; ac...gain.imag = -1.0"Wk AC\_GAIN(dnlcap, dnlcap) = ac. gain

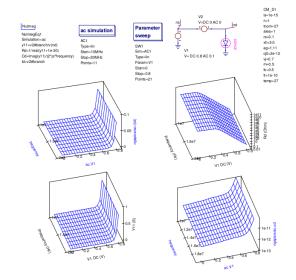

### Qucs-0.0.19-S-RC6 XSPICE Code Modeling Package: Part VII XSPICE Diode Model - (d) The Diode Small Signal AC performance; Y parameter, Rd and Cd Extraction

34 / 40

# Qucs-0.0.19-S-RC6 XSPICE Code Modeling Package: Part V XSPICE Diode Model - (e) The Diode Id/Vd Temperature Variation

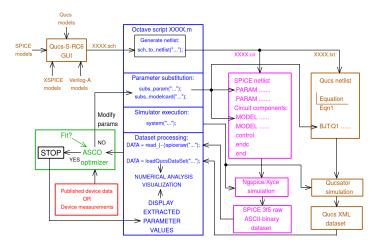

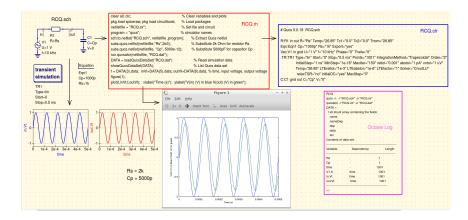

Qucs-0.0.19-S-RC6/Ngspice/Xyce Circuit Analysis and Compact Device Parameter Extraction from Maufacturer's Data or Measurements Controlled by Octave Script Files: Part I Structure Diagram

Qucs-0.0.19-S-RC6/Ngspice/Xyce Circuit Analysis and Compact Device Parameter Extraction from Maufacturer's Data or Measurements Controlled by Octave Script Files: Part II Octave Package

- The main purposes of Octave integration are:

- Parameter substitution in Qucs and SPICE netlists,

- Simulation process control from Octave,

- Simulator output dataset (SPICE3f5-raw and Qucs XML) loading into Octave matrix structures,

- Compact model parameter extraction from simulation and manufacturer's, or measured, data using curve fitting and optimization with the ASCO package.

- Example Octave package functions:

- subs\_spice\_netlist(FILE, PARAM, VALUE),

- subs\_qucs\_netlist(FILE, PARAM, VALUE),

- subs\_spice\_model\_netlist(FILE, MODEL, PARAM, VALUE),

- DATA = read\_spiceraw(FILE).

Where FILE - represents SPICE or Qucs netlist files

PARAM - represents a SPICE or Qucs variable or .MODEL parameter name

VALUE - represents a parameter value to replace its original quantity

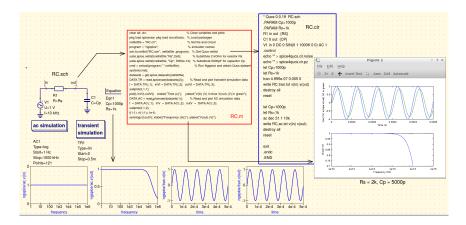

Qucs-0.0.19-S-RC6/Ngspice/Xyce Circuit Analysis and Compact Device Parameter Extraction from Maufacturer's Data or Measurements Controlled by Octave Script Files: Part III Simple Ngspice example

Qucs-0.0.19-S-RC6/Ngspice/Xyce Circuit Analysis and Compact Device Parameter Extraction from Maufacturer's Data or Measurements Controlled by Octave Script Files: Part IV Simple Qucs example

# Modeling of GaN HEMTs With Open Source Qucs-S Circuit Simulation and Compact Device Modelling Technology: Summary

- This presentation has attempted to show that open source compact modelling technology offers engineers and scientists viable tools for investigating the properties of emerging technology devices at a cost which is acceptable to all,

- Verilog-A models for GaN RF and power devices have been introduced and the problems involved in evaluating their performance demonstrated with a series of circuit simulation test benches,

- A short outline to the current state of Qucs-S development provided those attending the IEE EDS mini-Colloquium with a brief look at possible future directions in GPL circuit simulation and compact device modelling.

- Linux and Windows versions of Qucs-0.0.19-S-RC6 can be downloaded from: https://github.com/ra3xdh/qucs/releases/tag/0.0.19S-rc6

- Documentation is available here: https://qucs-help.readthedocs.org/en/spice4qucs/

- Octave packages from https://github.com/ra3xdh/octave\_circuittools/